# TLV320AIC3104 Programming Made Easy

David K. Wilson Audio Converter Products

#### **ABSTRACT**

The TLV320AlC3104 (AlC3104) is a versatile audio codec with multiple features. When first designing with the AlC3104, reading the entire data sheet and becoming familiar with the entire register set can be a daunting task. However, in many common configurations, it is possible to get the AlC3104 up and running while only writing to as few as 12 registers.

Although not intended to replace the data sheet, this document details several common configurations for the AlC3104. It gives a concise description of how to set up the codec and gives a script example that can be used to accelerate your design.

## 1 Controlling the AlC3104

All features of the AlC3104 are accessed by programmable registers. The registers can be programmed by an external microprocessor or DSP using  $I^2C^{TM}$  protocol. The master clock (MCLK) is not required to be running while programming the AlC3104. The fixed 7-bit  $I^2C$  address for the AlC3104 is 001 1000 (0x30h to write, 0x31h to read). The AlC3104 supports  $I^2C$  data rates up to 400 kHz.

It is good practice to perform a hardware reset after initial power up to ensure that all registers are in their default states and that the AIC3104 is ready to be programmed.

## 2 Determining Sample Rate and Master Clock Frequency

The first task for any design using the AlC3104 is to determine the desired sample rate and master clock frequency. With the exception of register programming, all internal timing, including the sample rate, is ultimately derived from an external master clock. By default, the ADC and DAC sample rates are MCLK/256. For the common audio sample rates 44.1 ksps and 48 ksps, the most common MCLK frequencies are 11.2896 MHz (44.1 ksps  $\times$  256) and 12.288 MHz (48 ksps  $\times$  256). If you are using one of these two MCLK frequencies and sample rates, no register programming is needed to set the sample rate.

Table 1 shows two common audio MCLK frequencies and the settings required to obtain common sample rates.

| DESIRED SAMPLE RATE | REGISTER SETTINGS                 |  |

|---------------------|-----------------------------------|--|

| MCLK = 11.2896 MHz  |                                   |  |

| 44.1 ksps           | None Required (use defaults)      |  |

| MOLIC 40 000 MILE   |                                   |  |

| MCLK = 12.288 MHz   |                                   |  |

| 48 ksps             | None Required (use defaults)      |  |

| 8 ksps              | Register 2, Page 0 = 0xAA         |  |

| 16 ksps             | Register 2, Page 0 = 0x44         |  |

| 32 ksps             | Register 2, Page 0 = 0x11         |  |

| 96 ksps             | Register 7, Page 0, D6 and D5 = 1 |  |

Table 1. MCLK Frequencies and Settings

I<sup>2</sup>C is a trademark of Koninklijke Philips Electronics NV.

If you do not have access to a common MCLK frequency, the AIC3104 also contains an internal PLL that can be used to set the timing. See the Audio Clock Generation section of the AIC3104 data sheet (SLAS510) for details on the usage of the PLL.

## 3 Selecting the Number of Bits and Digital Audio Format

Once the sample rate and MCLK have been selected, the number of bits and digital audio format can be selected. The default number of bits for the AlC3104 is 16 bits. The default digital audio format is I<sup>2</sup>S with the AlC3104 being the slave (Bit Clock and Word Clock as inputs to the AlC3104). The serial data format and number of bits are selected through Page 0, Register 9, and master or slave mode can be selected through Page 0, Register 8.

READ/ RESET BIT **DESCRIPTION** WRITE **VALUE** R/W D7 0 Bit Clock Directional Control 0: BCLK is an input (slave mode). 1: BCLK is an output (master mode). D6 R/W 0 Word Clock Directional Control 0: WCLK is an input (slave mode). 1: WCLK is an output (master mode).

Table 2. Page 0/Register 8: Audio Serial Data Interface Control Register A

Table 3. Page 0/Register 9: Audio Serial Data Interface Control Register B

| BIT    | READ/<br>WRITE | RESET<br>VALUE | DESCRIPTION                                                                                                                                                                                                               |

|--------|----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7-D16 | R/W            | 0              | Audio Serial Data Interface Transfer Mode 00: Serial data bus uses I <sup>2</sup> S mode. 01: Serial data bus uses DSP mode. 10: Serial data bus uses right-justified mode. 11: Serial data bus uses left-justified mode. |

| D5-D4  | R/W            | 0              | Audio Serial Data Word Length Control 00: Audio data word length = 16 bits 01: Audio data word length = 20 bits 10: Audio data word length = 24 bits 11: Audio data word length = 32 bits                                 |

## 4 Setting the Signal Path Through the AIC3104

The AIC3104 has been designed for low-power portable applications. As a result, when first powered up, the device defaults to a low-power mode with the codec largely powered down. The user must select a signal path through the AIC3104 and program the registers to enable the desired path.

The AIC3104 is versatile and has many different signal paths that can be selected. This application report covers only the most basic configurations. For a full description of the available signal paths, see the data sheet.

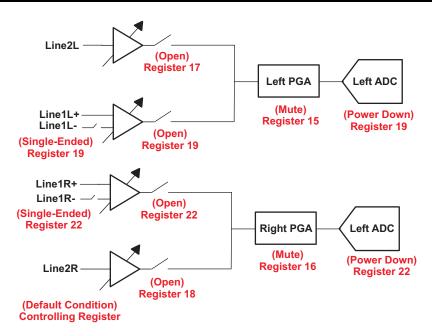

## 4.1 ADC

The ADC has two sets of stereo inputs, Line 1 Left and Right and Line 2 Left and Right. Line 1 Left and Right can be configured for single-ended or differential inputs (Figure 1). The default is single-ended with only the Plus (P) Inputs being used. Line 2 Left and Right are always single-ended. By default, none of the inputs is routed to the PGA. By default, both Left and Right PGAs are muted and the Left and Right ADCs are powered down.

Figure 1. ADC Stereo Inputs

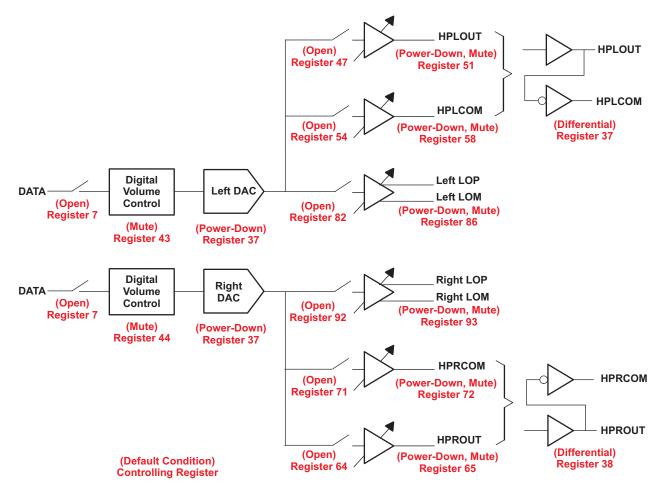

#### 4.2 DAC

The Left and Right DACs each have an independent digital volume control. By default, the DACs are powered down, and the volume controls are muted.

The outputs of the DACs can be routed to any of the four high-power outputs or the stereo, differential line-outputs. By default, the DACs are not routed to any output. Each of the outputs has an independent analog amplifier with volume control. By default, these are muted and powered down.

Four high-power outputs can be used in pairs to drive two differential 16- $\Omega$  loads or independently to drive up to four single-ended, 16- $\Omega$  loads. By default, these are configured for differential outputs.

The line-outs are always fully differential and are designed to drive high-Z (10- $k\Omega$ ) loads.

Figure 2. DAC Volume Control

## 5 Register Sequencing for Best Performance

In order to avoid unwanted audio artifacts associated with writing to the registers on the AIC3104, it is necessary to follow certain sequencing requirements. In some cases, the actual function of certain programming blocks depend on the register sequence to work properly.

Here are some guidelines:

- The ADC and DAC must be powered down when changing the sample rate.

- The PGAs must be muted before the ADC is powered down.

- When selecting an input, unmute the PGAs after routing the input and powering up the ADC.

- When selecting an output, power up and unmute the outputs after selecting the signal routing and powering up the DAC and unmuting the digital volume control.

www.ti.com Example Code

#### 6 Example Code

Format:

The following example code has been formatted to work with the AIC3104 EVM software GUI.

The following script makes maximum use of default settings to configure the AIC3104 for a single-ended stereo input into line 1 LP and RP, 16 bits, I<sup>2</sup>C, slave mode, 48-ksps sample rate to differential stereo out on the line-outs:

```

# MCLK = 12.288 MHz

# reset

W 30 01 08

# Route Line1LP to the Left ADC, Power up Left ADC

W 30 13 04

# Route Line1RP to the Right ADC, Power up Right ADC

W 30 16 04

# Unmute Left PGA, set gain to 0 dB

W 30 OF 00

# Unmute Right PGA, set gain to OdB

W 30 10 00

# Route Left data to Left DAC, Route Right data to Right DAC

W 30 07 0A

# Power up Left and Right DAC's

W 30 25 C0

\# Unmute Left digital volume control, set gain to 0 dB

W 30 2B 00

# Unmute Right digital volume control, set gain to 0 dB

W 30 2C 00

# Route Left DAC output to Left line outs

W 30 52 80

# Route Right DAC output to Right Line outs

W 30 5C 80

\# Power up Left line out \pm (differential), set gain to 0dB

\# Power up Right line out \pm (differential), set gain to 0 dB

W 30 5D 09

```

#### 7 Summary

The AlC3104 is a versatile device with many features. In addition to the features discussed in this document, the AlC3104 has an onboard PLL, programmable filters, many bypass paths, and the ability to route and switch signals to almost anywhere a designer may want. This application report is not a replacement for the TLV320AlC3104 data sheet. A thorough understanding of the data sheet can ensure that you get the best performance from the AlC3104.

In spite of the complexity of the AIC3104, it can also be quite simple to set up and use for many standard configurations.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

**Applications Products Amplifiers** amplifier.ti.com Audio www.ti.com/audio Data Converters Automotive www.ti.com/automotive dataconverter.ti.com DLP® Products Broadband www.dlp.com www.ti.com/broadband DSP Digital Control dsp.ti.com www.ti.com/digitalcontrol Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical Military Interface www.ti.com/military interface.ti.com Optical Networking Logic logic.ti.com www.ti.com/opticalnetwork Power Mgmt power.ti.com Security www.ti.com/security Telephony Microcontrollers microcontroller.ti.com www.ti.com/telephony Video & Imaging www.ti-rfid.com www.ti.com/video RF/IF and ZigBee® Solutions www.ti.com/lprf Wireless www.ti.com/wireless

> Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated