## Application Note **The Essential Guide for Developing With C2000™Real-Time Microcontrollers**

Matthew Pate

### ABSTRACT

Performance, efficiency, flexibility and protection – these are the attributes paramount to power electronics technologies, such as motor control, digital power, renewable energies, lighting, and electrical vehicles. Backed by over 20 years of working with customers developing real-time control applications, the C2000<sup>™</sup> real-time Microcontroller (MCU) platform enables developers to cost-efficiently meet all of the above criteria while also differentiating their designs. This application report is intended to provide a deeper look into the components providing differentiation to Real-Time Control Systems and give the next steps for evaluation.

## **Table of Contents**

| 1 C2000 and Real-Time Control                                                                       | 4                |

|-----------------------------------------------------------------------------------------------------|------------------|

| 1.1 Getting Started Resources                                                                       | 6                |

| 1.2 Processing                                                                                      | <mark>6</mark>   |

| 1.3 Control                                                                                         | 7                |

| 1.4 Sensing                                                                                         | <mark>8</mark>   |

| 1.5 Interface                                                                                       | 9                |

| 1.6 Functional Safety                                                                               | 10               |

| 2 Sensing Key Technologies                                                                          | 11               |

| 2.1 Accurate Digital Domain Representation of Analog Signals                                        | 11               |

| 2.2 Optimizing Acquisition Time vs Circuit Complexity for Analog Inputs                             | 13               |

| 2.3 Hardware Based Monitoring of Dual-Thresholds Using a Single Pin Reference                       | 15               |

| 2.4 Resolving Tolerance and Aging Effects During ADC Sampling                                       | 17               |

| 2.5 Realizing Rotary Sensing Solutions Using C2000 Configurable Logic Block                         | 1 <mark>8</mark> |

| 2.6 Smart Sensing Across An Isolation Boundary                                                      |                  |

| 2.7 Enabling Intra-Period Updates in High Bandwidth Control Topologies                              |                  |

| 2.8 Accurate Monitoring of Real-Time Control System Events Without the Need for Signal Conditioning |                  |

| 3 Processing Key Technologies                                                                       | 25               |

| 3.1 Accelerated Trigonometric Math Functions                                                        | 25               |

| 3.2 Fast Onboard Integer Division                                                                   |                  |

| 3.3 Hardware Support for Double-Precision Floating-Point Operations                                 |                  |

| 3.4 Increasing Control Loop Bandwidth With An Independent Processing Unit                           |                  |

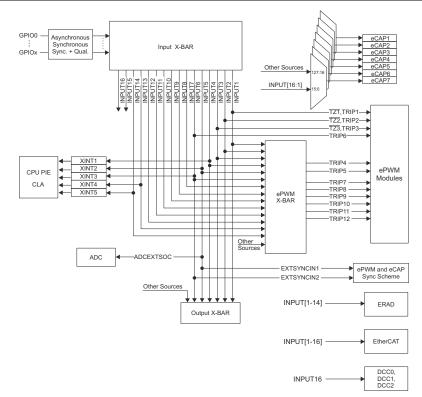

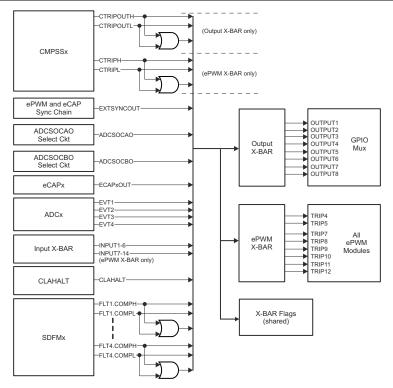

| 3.5 Flexible System Interconnect: C2000 X-Bar                                                       | 32               |

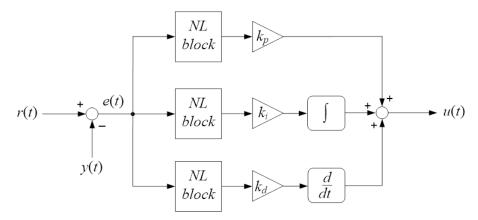

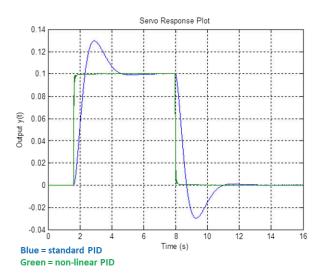

| 3.6 Improving Control Performance With Nonlinear PID Control                                        | 34               |

| 3.7 Understanding Flash Memory Performance In Real-Time Control Applications                        | <mark>36</mark>  |

| 3.8 Deterministic Program Execution With the C28x DSP Core                                          |                  |

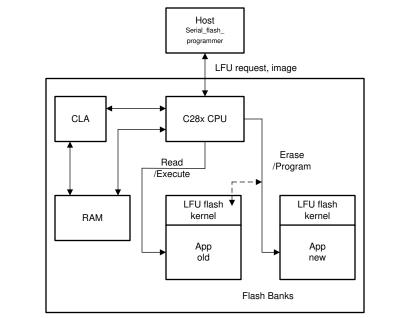

| 3.9 Efficient Live Firmware Updates (LFU) and Firmware Over-The-Air (FOTA) updates                  |                  |

| 4 Control Key Technologies                                                                          |                  |

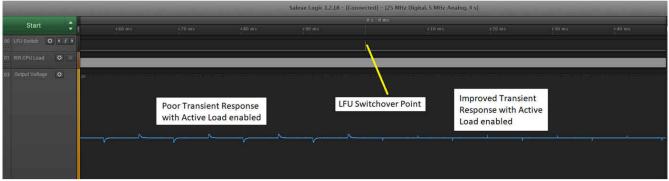

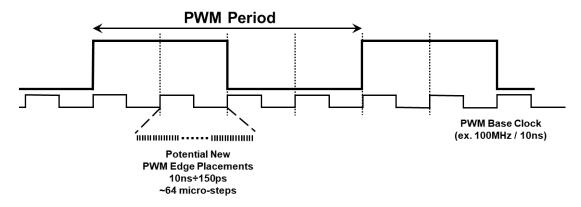

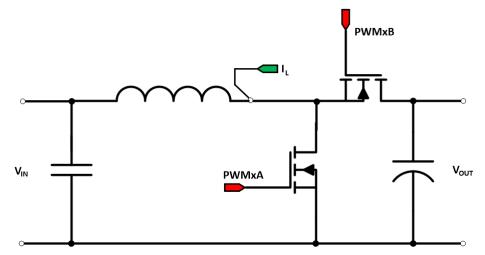

| 4.1 Reducing Limit Cycling in Control Systems With C2000 HRPWMs                                     |                  |

| 4.2 Shoot Through Prevention for Current Control Topologies With Configurable Deadband              |                  |

| 4.3 On-Chip Hardware Customization Using the C2000 Configurable Logic Block                         |                  |

| 4.4 Fast Detection of Over and Under Currents and Voltages                                          |                  |

| 4.5 Improving System Power Density With High Resolution Phase Control                               |                  |

| 4.6 Safe and Optimized PWM Updates in High-Frequency, Multi-Phase and Variable Frequency Topologies |                  |

| 4.7 Solving Event Synchronization Across Multiple Controllers in Decentralized Control Systems      |                  |

| 5 Interface Key Technologies                                                                        |                  |

| 5.1 Direct Host Control of C2000 Peripherals                                                        |                  |

| 5.2 Securing External Communications and Firmware Updates With an AES Engine                        | 59               |

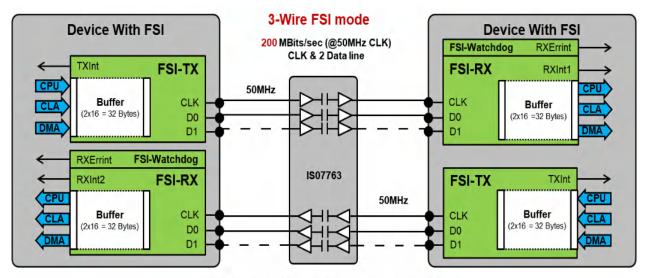

| 5.3 Distributed Real-Time Control Across an Isolation Boundary                          | 60              |

|-----------------------------------------------------------------------------------------|-----------------|

| 5.4 Custom Tests and Data Pattern Generation Using the Embedded Pattern Generator (EPG) |                 |

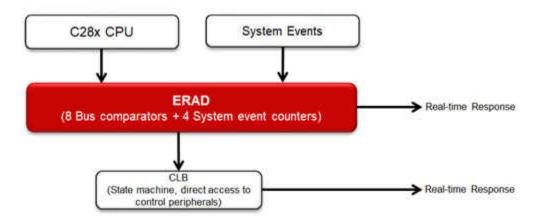

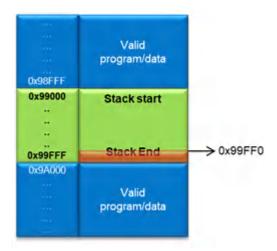

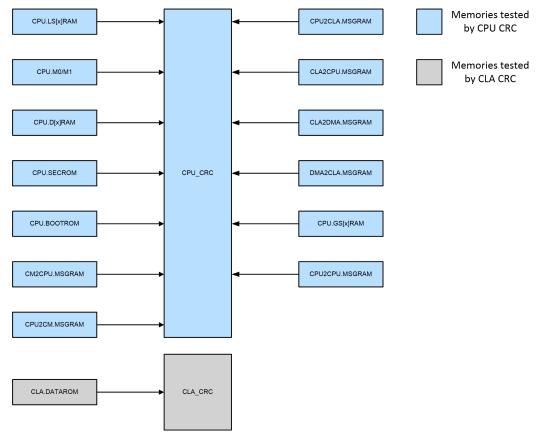

| 6 Safety Key Technologies                                                               | <mark>63</mark> |

| 6.1 Non-Intrusive Run Time Monitoring and Diagnostics as Part of the Control Loop       | <mark>63</mark> |

| 6.2 Hardware Built-In Self-Test of the C28x CPU                                         | <mark>65</mark> |

| 6.3 Zero CPU Overhead Cyclic Redundancy Check for Embedded On-Chip Memories             | <mark>66</mark> |

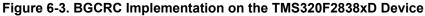

| 6.4 Boot Code Authentication Prior To Code Execution                                    | <mark>67</mark> |

| 7 References                                                                            | <mark>68</mark> |

| 7.1 Device List                                                                         | <mark>68</mark> |

| 7.2 Hardware/Software Resources                                                         | <mark>68</mark> |

| 7.3 Documentation                                                                       |                 |

| 8 Revision History                                                                      | <mark>69</mark> |

## List of Figures

| Figure 1-1. Common C2000 Real-Time Control Applications                                                                                 |                |

|-----------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Figure 1-2. C2000 Real-Time MCU Components                                                                                              | 4              |

| Figure 1-3. Real-Time Signal Chain Components                                                                                           | <mark>5</mark> |

| Figure 1-4. C2000 Processing                                                                                                            | 6              |

| Figure 1-5. PWM Block Diagram                                                                                                           | 7              |

| Figure 1-6. C2000 Analog Integration                                                                                                    |                |

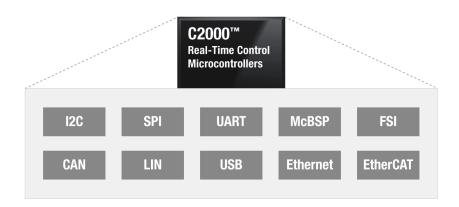

| Figure 1-7. C2000 MCU Supported Interfaces                                                                                              |                |

| Figure 1-8. Functional Safety Enablers                                                                                                  |                |

| Figure 2-1. Single-Ended Input Model                                                                                                    |                |

| Figure 2-2. Threshold Levels in a Hysteresis Controller                                                                                 |                |

| Figure 2-3. CMPSS Block Diagram                                                                                                         |                |

| Figure 2-4. ADC Post Processing Block on TMS320F2837xD.                                                                                 |                |

| Figure 2-5. Industrial Servo Drive With T-Format Absolute Position Encoder Interface                                                    |                |

| Figure 2-6. QepDIv Input and Output Diagram                                                                                             |                |

| Figure 2-7. Filter and Demodulator Inside the C2000 SDFM.                                                                               |                |

| Figure 2-8. SDFM Module With Both Primary and Secondary Filter Blocks on the TMS320F2837xD MCU                                          | 21             |

| Figure 2-9. Real-Time Signal Chain                                                                                                      | 22             |

| Figure 2-10. Intra-Period Update of PWM                                                                                                 |                |

| Figure 2-11. CMPSS Raw vs Filtered Output.                                                                                              |                |

| Figure 3-1. Park Transform                                                                                                              |                |

| Figure 3-2. TMU Improvement for Common Transforms                                                                                       |                |

| Figure 3-3. Truncated Division Function                                                                                                 |                |

| Figure 3-4. Floored Division Function                                                                                                   |                |

| Figure 3-5. Euclidean Division Function                                                                                                 |                |

| Figure 3-6. C28x and CLA Interfacing With the ADC and ePWM Modules                                                                      |                |

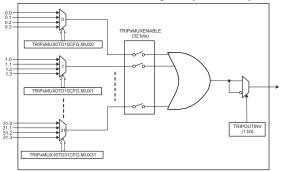

| Figure 3-7. Input X-Bar on the TMS320F2837xD MCU.                                                                                       |                |

| Figure 3-8. Local Mux and Logical OR on the TMS320F2837xD MCU                                                                           |                |

| Figure 3-9. X-Bar Sources and Destinations on the TMS320F2837xD MCU                                                                     |                |

| Figure 3-10. Non-Linear PID Block Diagram                                                                                               |                |

| Figure 3-11. Comparison of Response Time Between Linear and Non-linear PID                                                              |                |

| Figure 3-11. Comparison of Response Time Between Linear and Non-Intear Fib                                                              |                |

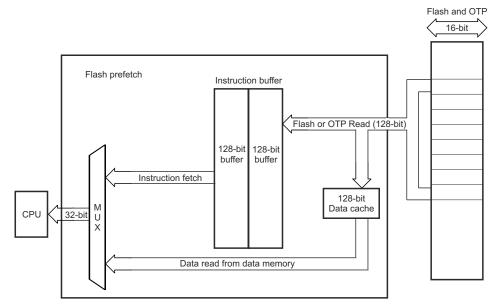

| Figure 3-12. C2000 Flash Freetch Module                                                                                                 |                |

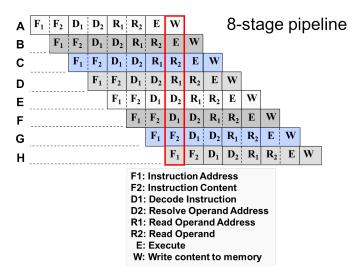

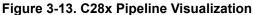

| Figure 3-13. C20x Pipeline Visualization<br>Figure 3-14. Standard Operation for a C28x CPU Maskable Interrupt                           |                |

| Figure 3-14. Standard Operation for a C20X CFO Maskable interrupt<br>Figure 4-1. HRPWM Capability vs Traditional PWM Generation Methods |                |

| Figure 4-1. HKF www.Capability vs. Traditional P. Www.Generation Methods                                                                |                |

| Figure 4-2. Synchronous Boost Controller<br>Figure 4-3. Cycle by Cycle Trip Action of the COMP Module With Configurable Deadband        | 40             |

| Figure 4-3. Cycle by Cycle The Action of the COMP Module With Configurable Deadband                                                     | 40             |

|                                                                                                                                         |                |

| Figure 4-5. CLB Configuration Tool in SysConfig.                                                                                        |                |

| Figure 4-6. CMPSS Visualization.                                                                                                        |                |

| Figure 4-7. Dual Active Bridge Block Diagram                                                                                            |                |

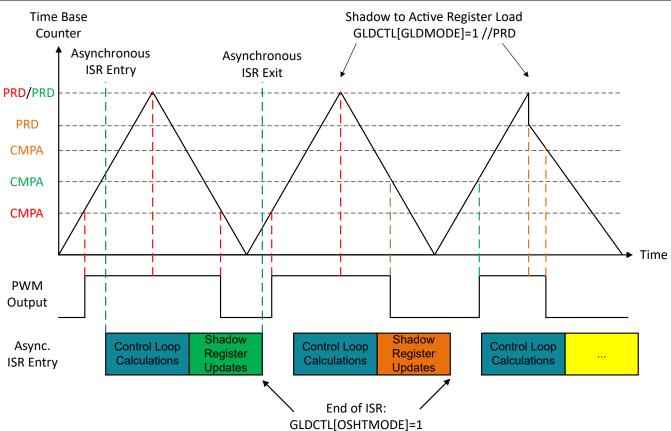

| Figure 4-8. Shadow to Active Load Action                                                                                                |                |

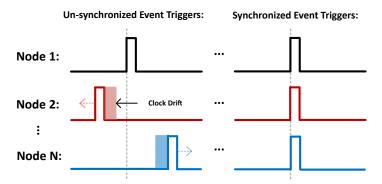

| Figure 4-9. Un-synchronized vs Synchronized Event Triggers.                                                                             | 55             |

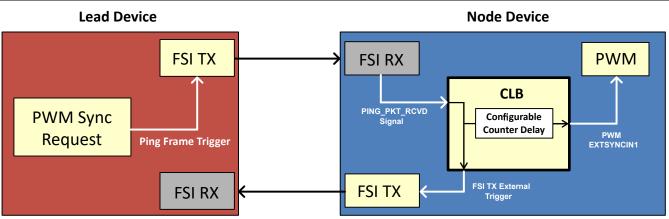

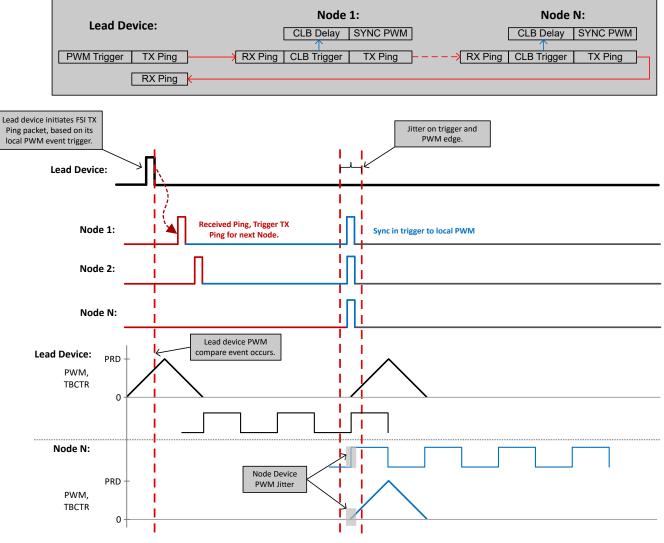

| Figure 4-10. Lead and Node Device Implementation                                                                                        |                |

| Figure 4-11. Daisy Chain Network Synchronization and Timing                                                                             |                |

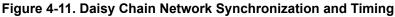

| Figure 5-1. HIC Bridge for FSI Applications.                                                                                            |                |

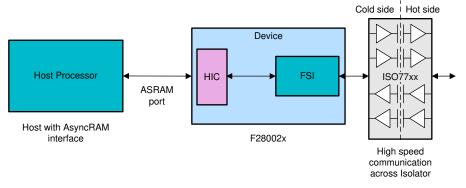

| Figure 5-2. HIC Bridge for Position Encoder Applications.                                                                               |                |

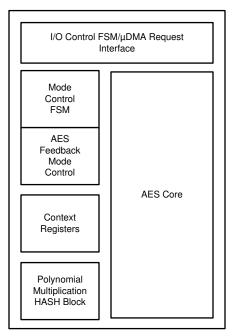

| Figure 5-3. AES Block Diagram.                                                                                                          |                |

| Figure 5-4. Full Duplex 3-Wire FSI Implementation                                                                                       |                |

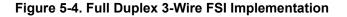

| Figure 5-5. FSI Skew Compensation                                                                                                       | 61             |

| Figure 5-6. Clocks with Offset                               | 62 |

|--------------------------------------------------------------|----|

| Figure 5-7. Serial Stream and Clock                          |    |

| Figure 6-1. ERAD Block Diagram                               |    |

| Figure 6-2. Stack Overflow Protection                        | 64 |

| Figure 6-3. BGCRC Implementation on the TMS320F2838xD Device |    |

| Figure 6-4. CMAC Operation                                   | 67 |

## List of Tables

| Table 2-1. TMS320F28379D 16-Bit ADC Specifications                                | 12 |

|-----------------------------------------------------------------------------------|----|

| Table 2-2. Range of Acquisition Time Configuration (per Channel)                  | 14 |

| Table 2-3. Typical Resistor Tolerance Over Time and System Impact                 |    |

| Table 2-4. Potential Phase Error Caused by Sample Delay                           |    |

| Table 3-1. TMU Supported Instructions Summary                                     | 26 |

| Table 3-2. Integer Division With and Without the FID Module                       |    |

| Table 3-3. Cycle Comparison Between FPU64 and FPU32                               | 30 |

| Table 3-4. Data Type Size C28x vs Arm                                             | 30 |

| Table 3-5. Effective Flash Access Times With Prefetch Enable                      | 37 |

| Table 4-1. Resolution for PWM vs HRPWM                                            | 44 |

| Table 4-2. Comparison of Fault Detection and Trip Methods                         | 49 |

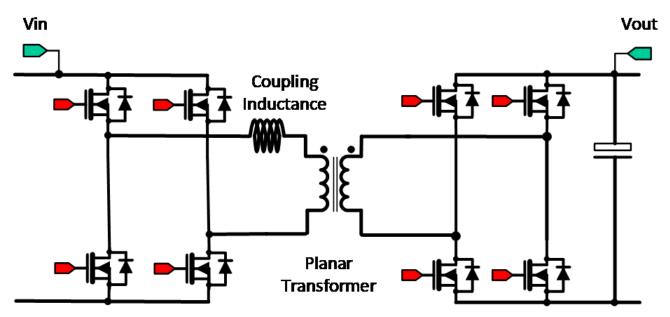

| Table 4-3. Phase Shift Requirements to Meet 1% Output Tolerance in a DAB Topology |    |

| Table 6-1. HWBIST Supported Diagnostic Coverage by Device                         |    |

|                                                                                   |    |

## Trademarks

C2000<sup>™</sup> and Code Composer Studio<sup>™</sup> are trademarks of Texas Instruments.

Bosch<sup>™</sup> is a trademark of Robert Bosch GmbH, Germany.

$\label{eq:arms} Arm^{\texttt{R}} \text{ is a registered trademark of } Arm \ Limited \ (or \ its \ subsidiaries) in the US \ and/or \ elsewhere.$

All trademarks are the property of their respective owners.

## 1 C2000 and Real-Time Control

Starting in 1997, Texas Instruments integrated flash memory, an Analog-to-Digital Converter (ADC), a Digital Signal Processor (DSP), and Pulse Width Modulation (PWM) units on a single device. The first C2000 real-time control MCU was born.

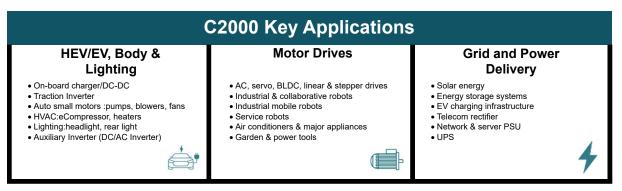

Over more than two decades, this device family grew and now millions of C2000's can be found in numerous applications in industrial and automotive applications like Motor Control, Solar Inverters, Digital Power, Electrical Vehicles and more (see Figure 1-1). There is one tie that binds all the above applications; their real-time nature and the need for a real-time controller.

Figure 1-1. Common C2000 Real-Time Control Applications

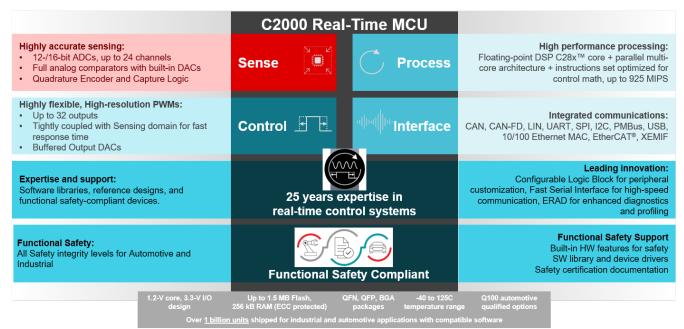

A real-time control system is typically composed of four main elements: see Figure 1-2:

- **Sensing:** or feedback acquisition. The application needs to measure several key parameters (voltage, current, motor speed, temperature) in an accurate manner and at a very precise moment in time.

- **Processing:** Use the sensing information to apply control algorithms to the incoming data and calculate the next output command.

- **Control:** The command is applied to the system, typically via a PWM unit driving the power electronics system, for example, the motor turns faster, the current to the solar installed system is reduced, the car is accelerating.

- Interface: The ability of the device to communicate to other external components. While not necessarily involved in the control of the system, communications to other system components also has to co-exist with the main control loop.

## Figure 1-2. C2000 Real-Time MCU Components

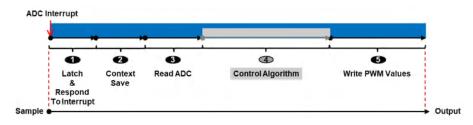

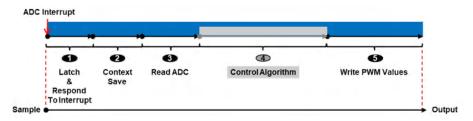

The key to real-time control is to minimize the time between Sensing, Processing and Control: this time is defined as the Real-Time Signal Chain. Figure 1-3 illustrates how the entire process is critical to understand the overall system performance of a real-time controller, vs simply looking at the time it takes the main processing unit to complete the control algorithm (step 4).

Figure 1-3. Real-Time Signal Chain Components

Many benchmarks, only focus on the time is takes to complete the step 4, typically expressed in Millions Instructions Per Second (MIPS) while the real-time challenge for designers is to minimize the time between Sample to Output: the real-time MCU architecture choice is critical.

The C2000 real-time MCU is a scalable, ultra-low latency, real-time controller platform designed for efficiency in power electronics, such as high power density, high switching frequencies, GaN and SiC technologies and was designed with the best Real-Time Signal Chain performance in mind and can deliver 2-times more real-time signal chain performance than an Arm<sup>®</sup>-based architecture.

The following sections showcase these advantages in terms of CPU cycle counts for easy comparison:

- Section 3.1

- Section 3.7

For more detailed information on the advantages C2000 brings to the real-time signal chain, including SW benchmarks, see *Signal Chain Benchmarking* - *A Demonstration of Optimized Real-time Performance of C2000*<sup>™</sup> *MCU*.

The next sections will zoom in each key elements that enables C2000 MCUs to deliver the best real-time signal performance in the market. Backed up with 25 years of expertise, which has translated in the largest reference design offering for power conversion in the industry, coming with robust production ready software and open source hardware documentation, designers can now innovate to and build energy system of the future. The C2000 real-time MCU continues to expand with a platform of software compatible device from the low-end to the high-end. Check the home page on TL com and register for the TL newsletter to stay up to date on new innovations from C2000 real-time MCUs.

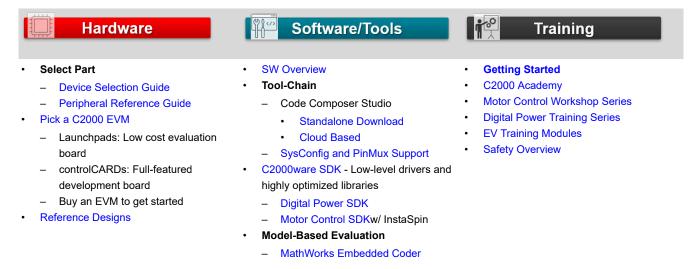

## **1.1 Getting Started Resources**

## **1.2 Processing**

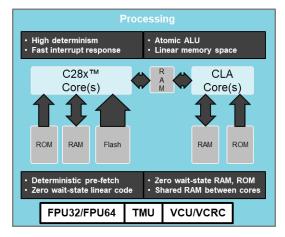

As seen in Figure 1-4, the C2000 real-time MCU uses the C28x DSP(Digital Signal Processor) core as the main processing unit. Capable of both 32-bit float or fixed point operations with dedicated instructions tailored to real-time control applications. Additional components of this sub-system are outlined below:

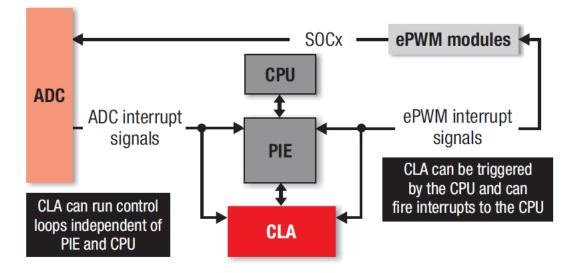

- Section 3.4: A state machine based 32-bit floating point co-processor capable of independent code execution from the main C28x DSP core

- C28x Extended Instructions:

- Floating Point Unit (FPU): Supporting 32-bit floating point operations and on select devices supports Section 3.3

- Section 3.1: Provides intrinsic instructions to support common trigonometric math functions commonly found in transfroms and torque loop calculations.

- Viterbi and CRC Unit(VCU): Reducing cycle count for both Viterbi and Cyclical Redundancy Check(CRC) operations found in complex math equations.

Figure 1-4. C2000 Processing

## 1.3 Control

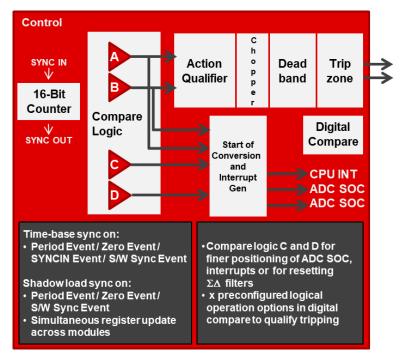

The control sub-system includes modules that will stimulate the system under control. Typically, this is done with Pulse Width Modulation (PWM) outputs. This could also be the output of the on-chip Digital-to-Analog Converter (DAC) or just a General-Purpose Input/Output (GPIO) pin.

- PWM Principle actuation module on the C2000 real-time MCU. Responsible for driving the external Field Effect Transistors (FETs) that exist in most power electronics systems. Supports both standard and high resolution modes for duty-cycle, period, and dead-band control of the waveform

- All PWMs on a given C2000 have global load capability, ensuring synchronous updates across multiple switch controls

- High resolution (~150ps) edge placement helps reduce limit cycling in control systems. Available for duty cycle, phase, and deadband placement.

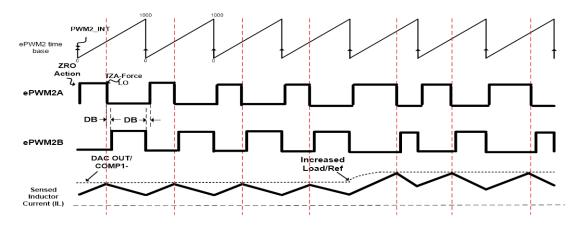

- Tightly coupled with the analog comparators to provide over voltage/current protectionCPU independent duty control for systems like Peak Current Mode Control as well as CPU independent duty control for systems like Peak Current Mode Control.

- Buffered DAC 12-bit DAC capable of driving a defined external load. Typically used to create a bias voltage in the analog domain.

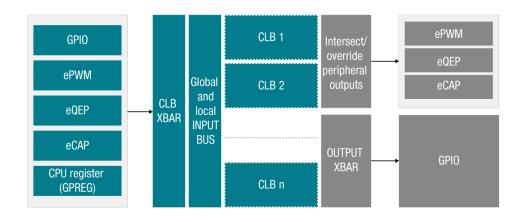

- Configurable Logic Block (CLB) Group of look up tables and state machine logic that operates on internal signal nodes in the hardware domain. Can be an endpoint or intermediary step to realize increased system performance.

Figure 1-5. PWM Block Diagram

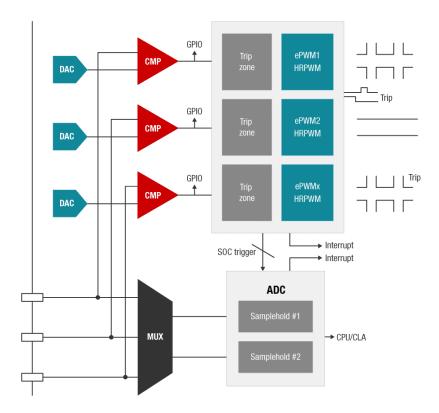

## 1.4 Sensing

The sensing sub-system includes modules that translate the state of the external system under control (analog domain) into data usable by the C2000 real-time controller (digital domain). Often this is the work of the Analog-to-Digital Converters (ADCs) on the MCU, but could also be handled by comparators or demodulators for external ADCs. Other unit converters are included in this domain, such as quadrature encoders and time pulse measurement devices.

- ADC Multiple 12 or 16-bit ADCs that are used primarily to convert the voltage or current (through a shunt) of the controlled system into the digital domain. Both an internal reference or external references are supported, with sample rates of 3.5MSPS (12-bit) and 1MSPS (16-bit) to quickly translate the system conditions to information that the control system can act upon.

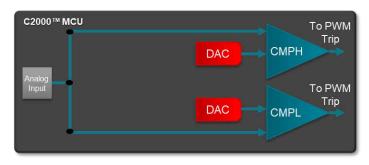

- Comparator (COMP) Multiple on-chip comparators provide system protection as well as cycle by cycle PWM control by comparing a system voltage to an internal reference point(generated by the internal 12-bit DACs). Direct connection to the ePWM modules exist to change the output state as quickly as possible without need for CPU intervention.

- Sigma Delta Demodulator On-chip logic used to decode the serial bit stream output from external sigma delta ADCs. Often used to cross the isolation boundary of high power systems. Includes hardware threshold detection.

- Quadrature Encoder Pulse Measurement (eQEP) Counts pulses from a variety of encoders to determine motor shaft position. Can be coupled with the CLB module for customer encoder solutions in HW.

- Time Capture (eCAP) Measures the time duration between external pulse events, useful for evaluating Hall Sensors. Both standard and high resolution modes are available.

## 1.5 Interface

An additional block that, while not typically associated with the real-time control loop of the system, is almost always needed from a system integration point of view. Good integration of the interface block with the CPU is essential to avoid high overhead that could impact the control loop. From serial data streams to multi-channel inputs, as well as industry standard options to proprietary formats, the interface sub-system supports a wide array of communications options.

- Controller Area Network (CAN) The CAN module supports the Bosch<sup>™</sup> CAN protocol standard.

- External Memory InterFace (EMIF) Parallel data bus typically used to support connections to SDRAM as well as wide bus peripherals.

- EtherCAT Slave Controller (EtherCAT) This module allows for the C2000 MCU to act as a slave node in an EtherCAT network.

- Ethernet 10/100 Mbps Ethernet controller and physical interface for external communications across this bus.

- Fast Serial Interface (FSI) 2 or 3 line simplex serial data transmit or receive. Designed to meet both the high speed (100Mbps) as well as the variable latency introduced when crossing an isolation boundary.

- · Host Interface Controller (HIC) Grants ability for other devices to control/interact with the C2000 peripherals

- Inter-Integrated Circuit (I2C) Interface/controller for an I2C bus

- Serial Peripheral Interface (SPI) Interface/controller for a standard Serial Peripheral Interface bus.

- Universal Asynchronous Receiver/Transmitter (UART) Interface/controller for Universal Asynchronous Receiver Transmitter bus

- Universal Serial Bus (USB) USB 2.0 MAC and PHY used to interface to standard USB network.

### Figure 1-7. C2000 MCU Supported Interfaces

### Note

Peripheral counts, as well as features, may vary from device to device. For a complete listing of the number of a peripherals on a device, see the data sheets referenced at the end of each section. For the feature sets supported on a given device, see the *C2000 Real-Time Control Peripherals Reference Guide*.

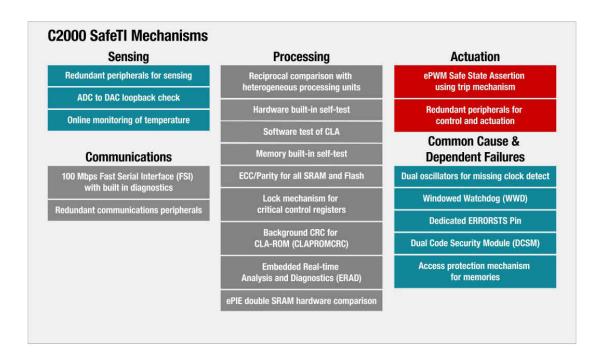

## **1.6 Functional Safety**

According to the International Electrotechnical Commission (IEC), safety is defined as freedom from unacceptable risk of physical injury or damage to thehealth of people, either directly or indirectly, as a result of damage to property or to the environment. The IEC defines functional safety as the part of overall safety that depends on a system or equipment operating correctly in response to its inputs.

With over 300 safety mechanisms defined and independently assessed by TUV SUD for its effectiveness, C2000 MCUs provide the required diagnostic coverage to meet a random hardware capability of SIL 2/ASIL B at a component level. Functional safety manuals provide detailed information on the safety mechanisms, techniques for achieving non-interference between elements and avoiding dependent failures, to aid customers in the development of compliant systems up to SIL 3/ASIL D.

Examples of functional safety enablers across the C2000 device can be seen in Functional Safety Enablers.

### Figure 1-8. Functional Safety Enablers

For more detailed information please see the following technical documents:

- Industrial Functional Safety forC2000<sup>™</sup> Real-Time Microcontrollers

- Automotive Functional Safety forC2000<sup>™</sup> Real-Time Microcontrollers

## 2 Sensing Key Technologies

## 2.1 Accurate Digital Domain Representation of Analog Signals

### 2.1.1 Value Proposition

Many MCUs have integrated ADCs as part of their sensing subsystem. The ability of the ADC to accurately convert the analog domain to the digital space is one of the most crucial aspects of the MCU in order to realize a proper control system. The data sheet specifications for a C2000 MCU ADC are such that performance in the system can be properly evaluated prior to system implementation.

### 2.1.2 In Depth

The first step when selecting an MCU for a real-time control system is relatively straightforward process; comparing the components of the MCU to the system needs. There are questions of memory size, CPU speed, communications standards used, analog content, number of I/Os, and so forth. When looking at the fit for an analog module like the ADC, it can appear straightforward to base the decision on sampling rate, number of inputs, and bit level. In practice, however, there is much more to this decision.

Too often ADC selection is based solely on the top level specifications, only to realize during development there are limitations to the system performance due to the ADC itself:

- Will the system be using the analog inputs for frequency analysis? Then, AC specifications like SNR and THD become important to consider when picking an MCU with an on-chip ADC.

- Is overall accuracy a key care about? Looking at the DC specifications like INL, Gain, and Offset are key

parameters to consider.

A quick summary of ADC specifications and their relevance to the system:

- AC Specifications: Parameters related to how accurately the converter can resolve the fundamental frequency tone of a signal from other noise sources. Includes SNR, SINAD, THD, and SFDR all expressed in dB. Also includes ENOB, which is the SINAD translated into number of bits. Typically SINAD and ENOB based on SINAD are considered when choosing an ADC, the importance will vary depending on the end application.

- DC Specifications: Parameters related to the accuracy of the converter as it applies to representing an analog input in the digital domain. Includes Gain, Offset, DNL, and INL. The weighted summation of the Gain, Offset, and INL are often referred to as "Total Unadjusted Error" (Equation 1). This equation is typically used to determine the real-world impact of these parameters on the accuracy of a conversion.

$$\sum \sqrt{(\text{Err}_{\text{gain}})^2 + (\text{Err}_{\text{offset}})^2 + (\text{Err}_{\text{INL}})^2}$$

(1)

### where

- Err<sub>gain</sub> is the maximum gain error of the ADC in LSBs

- Err<sub>offset</sub> is the maximum offset error ADC in LSBs

- Err<sub>INL</sub> is the maximum INL error of the ADC in LSBs

An example of how the C2000 ADC is specified and the parameters can be seen in Table 2-1, a dynamic link to this same table in the data sheet is located here.

One final aspect of all the parameters that C2000 devices list in the data sheet is what is implied by the inclusion of the parameter itself. For parameters that have a MIN/MAX, these are assured specs over the full operational range and lifetime of the device. The typical (TYP) column is also significant for all parameters, as it represents the mean performance of a parameter across its operational range.

| Parameter                                                     | Test Conditions                                                            | Min              | Тур              | Max  | Unit    |

|---------------------------------------------------------------|----------------------------------------------------------------------------|------------------|------------------|------|---------|

| ADC conversion cycles                                         |                                                                            | 29.6             |                  | 31   | ADCCLKs |

| Power-up time (after setting<br>ADCPWDNZ to first conversion) |                                                                            |                  |                  | 500  | μs      |

| Gain error                                                    |                                                                            | -64              | ±9               | 64   | LSBs    |

| Offset error                                                  |                                                                            | -16              | ±9               | 16   | LSBs    |

| Channel-to-channel gain error                                 |                                                                            |                  | ±6               |      | LSBs    |

| Channel-to-channel offset error                               |                                                                            |                  | ±3               |      | LSBs    |

| ADC-to-ADC gain error                                         | Identical $V_{REFHI}$ and $V_{REFLO}$ for all ADCs                         |                  | ±6               |      | LSBs    |

| ADC-to-ADC offset error                                       | Identical $V_{REFHI}$ and $V_{REFLO}$ for all ADCs                         |                  | ±3               |      | LSBs    |

| DNL                                                           |                                                                            | > -1             | ±0.5             | 1    | LSBs    |

| INL                                                           |                                                                            | -3               | ±1.5             | 3    | LSBs    |

| SNR                                                           | V <sub>REFHI</sub> = 2.5 V, f <sub>in</sub> = 10 kHz                       |                  | 87.6             |      | dB      |

| THD                                                           | V <sub>REFHI</sub> = 2.5 V, f <sub>in</sub> = 10 kHz                       |                  | -93.5            |      | dB      |

| SFDR                                                          | V <sub>REFHI</sub> = 2.5 V, f <sub>in</sub> = 10 kHz                       |                  | 95.4             |      | dB      |

| SINAD                                                         | V <sub>REFHI</sub> = 2.5 V, f <sub>in</sub> = 10 kHz                       |                  | 86.6             |      | dB      |

|                                                               | V <sub>REFHI</sub> = 2.5 V, f <sub>in</sub> = 10 kHz,<br>single ADC        |                  | 14.1             |      |         |

| ENOB                                                          | V <sub>REFHI</sub> = 2.5 V, f <sub>in</sub> = 10 kHz,<br>synchronous ADCs  |                  |                  | bits |         |

|                                                               | V <sub>REFHI</sub> = 2.5 V, f <sub>in</sub> = 10 kHz,<br>asynchronous ADCs | Not<br>supported |                  |      |         |

| PSRR                                                          | V <sub>DDA</sub> = 3.3-V DC + 200 mV<br>DC up to Sine at 1 kHz             |                  | 77               |      | dB      |

| PSRR                                                          | V <sub>DDA</sub> = 3.3-V DC + 200 mV<br>Sine at 800 kHz                    |                  | 74               |      | dB      |

| CMRR                                                          | DC to 1 MHz                                                                |                  | 60               |      | dB      |

| V <sub>REFHI</sub> input current                              |                                                                            |                  | 190              |      | μA      |

|                                                               | V <sub>REFHI</sub> = 2.5 V, synchronous ADCs                               | -2               |                  | 2    |         |

| ADC-to-ADC isolation                                          | V <sub>REFHI</sub> = 2.5 V, asynchronous ADCs                              |                  | Not<br>supported |      | LSBs    |

### Table 2-1. TMS320F28379D 16-Bit ADC Specifications

### 2.1.3 Device List

- TMS320F2838xD/S

- TMS320F2837xD/S

- TMS320F2807x

- TMS320F28004x

- TMS320F28003x

- TMS320F28002x

- TMS320F280013x

- TMS320F280015x

### 2.1.4 Hardware Platforms and Software Examples

All controlCARDs for their specific C2000 MCU have been verified to reproduce the DS specifications for the on-chip ADC

- TMDSCNCD28388D

- TMDSCNCD28379D

- TMDSCNCD280049C

- TMDSCNCD280025

- TMDSCNCD2800137

- TMDSCNCD2800157

### 2.1.5 Documentation

- Texas Instruments: TMS320F2838x Real-Time Microcontrollers With Connectivity Manager Data Sheet (see the C28x Analog Peripherals section)

- Texas Instruments: TMS320F2837xD Dual-Core Microcontrollers Data Sheet (see the Analog Peripherals section)

- Texas Instruments: TMS320F28004x Microcontrollers Data Sheet (see the Analog Peripherals section)

- Texas Instruments: TMS320F28003x Microcontrollers Data Sheet (see the Analog Peripherals section)

- Texas Instruments: TMS320F28002x Microcontrollers Data Sheet (see the Analog Peripherals section)

- Texas Instruments: TMS320F280013x Microcontrollers Data Sheet(see the Analog Peripherals section)

- Texas Instruments: TMS320F280015x Microcontrollers Data Sheet (see the Analog Peripherals section)

## 2.2 Optimizing Acquisition Time vs Circuit Complexity for Analog Inputs

### 2.2.1 Value Proposition

Control systems have the need to interface with a variety of feedback and monitoring sources. Signal sources in these systems differ in their ability to drive a capacitive input circuit like those typically found in the sampleand-hold (S+H) input circuit of an analog-to-digital converter (ADC). The ADCs on C2000 devices allow the acquisition time of the S+H to be individually configured for each input channel over a wide range. This allows the system to simultaneously interface with a mix of high-performance and low-cost signal sources.

### 2.2.2 In Depth

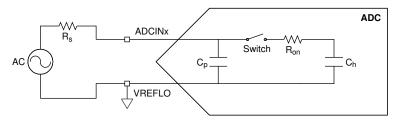

The inputs of an ADC are typically modeled as a switched capacitor circuit where the hold capacitor inside the ADC,  $C_h$ , needs to be charged from an unknown voltage to a value close to the input voltage during the acquisition time. An example, taken from the TMS320F2837xD device, is shown in Figure 2-1.

Figure 2-1. Single-Ended Input Model

The required acquisition time for charging  $C_h$  is determined by the external impedance of passive components, bandwidth of any buffers or sensors, the internal ADC input parasitics, and the resolution of the ADC.

The system designer can make a variety of trade-offs with respect to external circuit cost and complexity vs settling speed, for example:

- Adding/upgrading the op-amp buffer driving the ADC inputs: Lowering acquisition time through better charge transfer to the sample and hold capacitor inside the ADC

- Increasing the amount of resistance and/or capacitance seen by the ADC input: Helps reduce noise by adding additional low-pass filtering at the expense of a longer acquisition time

- **Tolerating less accuracy:** Alternatively, using a smaller acquisition window to decrease the sampling time, at the expense of accuracy/resolution.

With all the above possible trade-offs, it is difficult to select a single acquisition time that is appropriate for all analog inputs in the system. C2000 ADCs allow a separate acquisition window to be selected for each channel, giving the system designer a great deal of flexibility to make whatever speed vs signal conditioning circuit cost vs accuracy trade-offs they would like.

The acquisition window (controlled by the ACQPS field of the ADC SOC configuration register) can also be configured over a wide range of values and with a small step size as shown in Table 2-2.

| C2000 MCU                                                            | Device<br>SYSCLK | Minimum S+H Time | Maximum S+H<br>Time | S+H Time Configuration<br>Resolution |

|----------------------------------------------------------------------|------------------|------------------|---------------------|--------------------------------------|

| TMS320F28004x and<br>TMS320F28002x                                   | 100 MHz          | 80 ns            | 5.1 µs              | 10.00 ns                             |

| TMS320F2807x,TMS320F28003<br>x<br>,TMS320F280013x,<br>TMS320F280015x | 120 MHz          | 75 ns            | 4.3 µs              | 8.33 ns                              |

| TMS320F2837xD and<br>TMS320F2837xS                                   | 200 MHz          | 75 ns            | 2.6 µs              | 5.00 ns                              |

### Table 2-2. Range of Acquisition Time Configuration (per Channel)

There are a variety of ways to model the ADC input, Texas Instruments offers free tools to help design the ADC input driver circuit as well as instructional videos on proper front end component selection.

### 2.2.3 Device List

- TMS320F2838xD/S

- TMS320F2837xD/S

- TMS320F2807x

- TMS320F28004x

- TMS320F28003x

- TMS320F28002x

- TMS320F280013x

- TMS320F280015x

### 2.2.4 Hardware Platforms and Software Examples

- TMDSCNCDF28388D

- TMDSCNCDF28379D

- TMDSCNCDF280049C

- TMDSCNCD280039C

- TMDSCNCD280025

- TMDSCNCD2800137

- TMDSCNCD2800157

- F2838xD ADC SW Example

- F2837xD ADC SW Example

- F28004x ADC SW Example

- F28002x ADC SW Example

- F280013x ADC SW Example

- F280015x ADC SW Example

### 2.2.5 Documentation

- Charge-Sharing Driving Circuits for C2000 ADCs

- ADC Input Circuit Evaluation for C2000 MCUs

- SAR ADC Input Driver Design

- TI Precision Labs ADCs: Introduction to SAR ADC Front-End Component Selection

- TMS320F2838xD Real-Time Microcontrollers Technical Reference Manual (for more information, see the Choosing an Acquisition Window Duration section)

- TMS320F2837xD Real-Time Microcontrollers Technical Reference Manual (for more information, see the Choosing an Acquisition Window Duration section)

- TMS320F28004x Real-Time Microcontrollers Technical Reference Manual (for more information, see the Choosing an Acquisition Window Duration section)

- TMS320F28003x Real-Time Microcontrollers Technical Reference Manual (for more information, see the Choosing an Acquisition Window Duration section)

- TMS320F28002x Real-Time Microcontrollers Technical Reference Manual (for more information, see the Choosing an Acquisition Window Duration section)

- TMS320F280013x Real-Time Microcontrollers Technical Reference Manual (for more information, see the Choosing an Acquisition Window Duration section)

- TMS320F280015x Real-Time Microcontrollers Technical Reference Manual (for more information, see the Choosing an Acquisition Window Duration section)

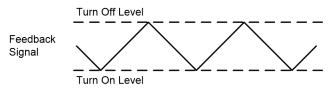

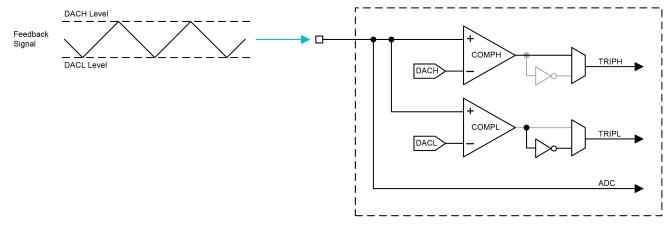

### 2.3 Hardware Based Monitoring of Dual-Thresholds Using a Single Pin Reference

### 2.3.1 Value Proposition

C2000 MCUs help to mitigate the cost and complexity of using multiple comparators to monitor a feedback signal by providing single pin access to two embedded voltage comparators per each Comparator Subsystem (CMPSS) module.

### 2.3.2 In Depth

Control systems commonly use voltage comparators to monitor feedback signals for threshold crossing events. These crossing events can represent a variety of states that range from nominal to critical conditions. A single feedback signal may sometimes be monitored by multiple comparators in order to trigger a custom response for each state.

Consider a simple hysteresis controller (Figure 2-2) that uses two threshold levels to define the actuation on-off behavior:

Figure 2-2. Threshold Levels in a Hysteresis Controller

- 1. A low-level "floor" threshold defines when the actuation should turn on, and

- 2. A high-level "ceiling" threshold defines when the actuation should turn off

A comparator-based monitoring and triggering scheme for this hysteresis controller can be implemented using a single CMPSS pin as shown in Figure 2-3. Similarly, a second CMPSS pin can be used to detect both over-voltage and under-voltage fault conditions for system protection.

Figure 2-3. CMPSS Block Diagram

Each CMPSS comparator is provided with its own voltage reference DAC, output conditioning logic, and unique trip signals for independent operation. Additionally, each CMPSS pin is also assigned to an ADC channel that can sample the pin voltage in parallel with comparator monitoring. These ADC samples can be used to influence sophisticated system behaviors, and to serve as a redundant form of voltage monitoring.

The multi-function capability of the CMPSS pin demonstrates a significant advantage in resource optimization over other embedded solutions with dedicated pin functionality; the optimization advantage is even greater when compared to discrete solutions that require localized resources like power supplies and reference voltages. System cost and complexity can be reduced by utilizing the full resources available from each C2000 MCU pin.

### 2.3.3 Device List

- TMS320F2838xD/S

- TMS320F2837xD/S

- TMS320F2807x

- TMS320F28004x

- TMS320F28003x

- TMS320F28002x

- TMS320F280013x

- TMS320F280015x

### 2.3.4 Hardware Platforms and Software Examples

- TIDM-DC-DC-BUCK

- TIDM-DC-DC-BUCK Example SW

- TIDM-02002

- TIDM-02002 Example SW

- TIDM-1022

- TIDM-1022 Software Example

- TMDXIDDK379D

- TMDXIDDK379D Software Examples

### 2.3.5 Documentation

- TMS320F2838x Real-Time Microcontrollers With Connectivity Manager Data Sheet (for more information, see the Comparator Subsystem (CMPSS) chapter)

- TMS320F2837xD Dual-Core Microcontrollers Data Sheet (for more information, see the Comparator Subsystem (CMPSS) section)

- TMS320F28004x Microcontrollers Data Sheet (for more information, see the Comparator Subsystem (CMPSS) section)

- TMS320F28003x Microcontrollers Data Sheet (for more information, see the Comparator Subsystem (CMPSS) section)

- TMS320F28002x Real-Time Microcontrollers Data Sheet (for more information, see the Comparator Subsystem (CMPSS) section)

- TMS320F280013x Real-Time Microcontrollers Data Sheet (for more information, see the Comparator Subsystem (CMPSS) section)

- TMS320F280015x Real-Time Microcontrollers Data Sheet(for more information, see the Comparator Subsystem (CMPSS) section)

- TMS320F2838xD Real-Time Microcontrollers Technical Reference Manual (for more information, see the Comparator Subsystem (CMPSS) chapter)

- TMS320F2837xD Real-Time Microcontrollers Technical Reference Manual (for more information, see the Comparator Subsystem (CMPSS) chapter)

- TMS320F28004x Real-Time Microcontrollers Technical Reference Manual (for more information, see the Comparator Subsystem (CMPSS) chapter)

- TMS320F28003x Real-Time Microcontrollers Technical Reference Manual (for more information, see the Comparator Subsystem (CMPSS) chapter)

- TMS320F28002x Real-Time Microcontrollers Technical Reference Manual (see the Comparator Subsystem (CMPSS) chapter)

- TMS320F280013x Real-Time Microcontrollers Technical Reference Manual (see the Comparator Subsystem (CMPSS) chapter)

- TMS320F280015x Real-Time Microcontrollers Technical Reference Manual(see the Comparator Subsystem (CMPSS) chapter)

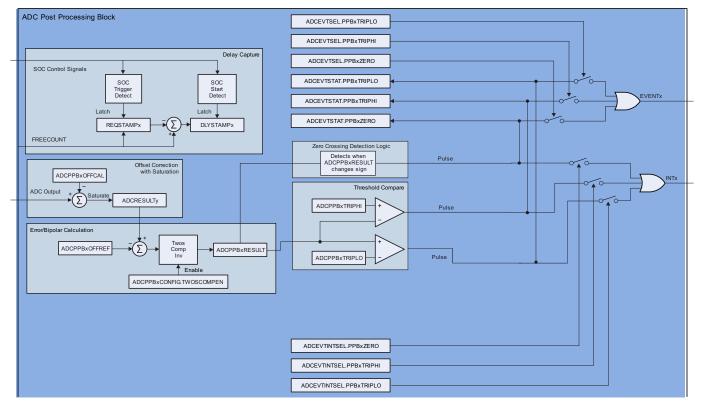

## 2.4 Resolving Tolerance and Aging Effects During ADC Sampling

### 2.4.1 Value Proposition

The ADC result is often manipulated mathematically before its used in the control law of a given system. This is typically done with some additional operations by the CPU, adding increased latency to the system as well as loading the CPU for such operations. The C2000 MCU as the ability to correct for this in hardware with no CPU overhead and no impact to ADC sample rate.

### 2.4.2 In Depth

Prior to using the ADC result in control calculations, it is often necessary to remove any known offset introduced by external factors such as component tolerances or layout differences (Table 2-3). While aspects of the above issues can be partially addressed through PCB layout or choosing higher tolerance/stable resistors there are always deviations from the ideal.

| Life Cycle Stage      | Total Tolerance | Associated 12-Bit Error |  |  |  |  |

|-----------------------|-----------------|-------------------------|--|--|--|--|

| Purchase              | ±0.05%          | ±2 LSBs                 |  |  |  |  |

| Post Assembly         | ±0.5%           | ±20 LSBs                |  |  |  |  |

| Post Storage/Moisture | ±0.75%          | ±30 LSBs                |  |  |  |  |

| Temp Coeff and EOL    | ±1.00%          | ± 40 LSBs               |  |  |  |  |

| Table 2-3. Typical | Posistor Tol  | oranco Ovor | Time and S | vetom Impact |

|--------------------|---------------|-------------|------------|--------------|

| Table 2-5. Typical | Resistor role | erance Over | Time and S | ystem impact |

C2000 MCUs implement an integrated hardware block to correct up to a 10-bit signed value co-incident to the ADC conversion process, saving valuable cycles in the system. The cycle value to the system is effectively doubled, as the ADC sample rate is maintained and no CPU cycles are used to perform the correction. Saturation is built in as well.

For the implementation of the offset correction in addition to the other modules included in the ADC Post Processing Block, see Figure 2-4.

Figure 2-4. ADC Post Processing Block on TMS320F2837xD

## 2.4.3 Device List

- TMS320F2838xD/S

- TMS320F2837xD/S

- TMS320F2807x

- TMS320F28004x

- TMS320F28003x

- TMS320F28002x

- TMS320F280013x

- TMS320F280015x

### 2.4.4 Hardware Platforms and Software Examples

- TMDSCNCDF28388D

- TMDSCNCDF28379D

- TMDSCNCDF280049C

- TMDSCNCD280039C

- TMDSCNCD280025

- TMDSCNCD2800137

- TMDSCNCD2800157

- F2838xD ADC PPB SW Example

- F2837xD ADC PPB SW Example

- F28004x ADC PPB SW Example

- F28003x ADC PPB SW Example

- F28002x ADC PPB SW Example

- F280013x ADC PPB SW Example

- F280015x ADC PPB SW Example

### 2.4.5 Documentation

- TMS320F2838xD Real-Time Microcontrollers Technical Reference Manual see the Post-Processing Blocks section in the Analog-to-Digital Converter (ADC) chapter

- TMS320F2837xD Real-Time Microcontrollers Technical Reference Manual see the Post-Processing Blocks section in the Analog-to-Digital Converter (ADC) chapter

- TMS320F28004x Real-Time Microcontrollers Technical Reference Manual see the Post-Processing Blocks section in the Analog-to-Digital Converter (ADC) chapter

- TMS320F28003x Real-Time Microcontrollers Technical Reference Manual see the Post-Processing Blocks section in the Analog-to-Digital Converter (ADC) chapter

- TMS320F28002x Real-Time Microcontrollers Technical Reference Manual see the Post-Processing Blocks section in the Analog-to-Digital Converter (ADC) chapter

- TMS320F280013x Real-Time Microcontrollers Technical Reference Manual see the Post-Processing Blocks section in the Analog-to-Digital Converter (ADC) chapter

- TMS320F280015x Real-Time Microcontrollers Technical Reference Manual -see the Post-Processing Blocks section in the Analog-to-Digital Converter (ADC) chapter

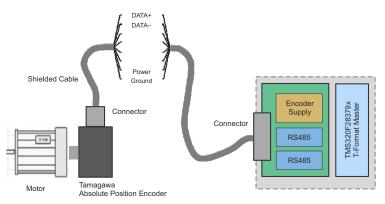

## 2.5 Realizing Rotary Sensing Solutions Using C2000 Configurable Logic Block

## 2.5.1 Value Proposition

As mentioned in the article: On-Chip Hardware Customization (Section 4.3), the C2000 Configurable Logic Block (CLB) technology enables systems designers to implement new logic within the C2000 device and eliminate external circuitry. A specific example for a real time control system is an integrated interface to digital rotary encoders; using the CLB, developers have the freedom to integrate an industry-standard encoder communications protocol or an application-specific customized protocol inside the C2000 MCU without additional external circuitry.

## 2.5.2 In Depth

A digital rotary encoder is a device that converts the position of a shaft to a digital signal. There are two main types of encoders:

- Absolute Encoders (Figure 2-5): The output of an absolute encoder indicates the current angular position in a message sent back to the master as defined by a particular protocol.

- Incremental Encoders: The output of an incremental encoder provides information in a train of modulated pulses that are typically further processed by the system master into information such as speed, distance and position.

Figure 2-5. Industrial Servo Drive With T-Format Absolute Position Encoder Interface

C2000 CLB technology enables an integrated solution to interface to the most popular digital rotary position encoders, eliminating the necessity for external field-programmable gate arrays (FPGAs) or application-specific integrated circuits (ASICs). The PositionManager BoosterPackplug-in module is a flexible low voltage platform intended for evaluating various encoder interfaces and designed to work with multiple C2000 LaunchPad development kits such as the LAUNCHXL-F28379D, LAUNCHXL-F280049C, or the LAUNCHXL-F280025C.

Below are examples of encoders that are available for evaluation today as part of the Motor Control SDK software package. Future updates are planned to add examples for both the BiSS-C and EnDAT22 protocols.

• T-Format Absolute Encoder Interface:

The Tamagawa T-Format protocol is a popular digital, bidirectional interface for absolute encoders. The easy-to-use library and example software delivered with TIDM-1011 demonstrates Tamagawa's T-Format standard. In this example, the T-Format absolute encoder interface is integrated into the C2000 using on-chip resources such as the CLB, SPI, and GPIO as shown in Figure 2-5. This TI Design includes the following features:

- A T-Format encoder interface library and CRC library that implements protocol commands

- A demonstration project (with full source code access) to exercise the T-Format commands

- Fully supported by the C2000 CLB Tool integrated inside Code Composer Studio

- T-Format Evaluation in High-Bandwidth Current Loop Applications:

With the recent C2000 MCUs such as TMS320F2837x and TMS320F28004x, it is possible to implement Fast Current Loop (FCL) algorithms that provide a high current loop bandwidth with the same external hardware as used in classical Field Oriented Control (FOC) methods. TI has developed the FCL algorithm on these MCUs and implemented it on the DesignDRIVE IDDK platform. The T-Format encoder interface has been integrated into an evaluation implementation of FCL algorithms on C2000 devices.

*Quick Response Control of PMSM Using Fast Current Loop* studies the frequency response analysis of current loops in real time and also verifies the interface logic for the T-format encoder interface implemented in TIDM-1011. The position loop in this example can be closed using a QEP encoder or a T-format encoder and FCL can be implemented in both cases.

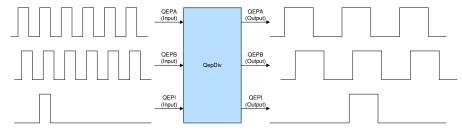

• Pulse Train Output (PTO) QepDiv and PulseGen:

Incremental rotary encoders output a pulse train to indicate that the shaft being monitored has moved. The system master typically processes this pulse train to determine information such as speed, distance and position. In the QepDiv implementation, position information is sent from the encoder to the Enhanced Quadrature Encoder Pulse (eQEP) module on a C2000 MCU. In the PulseGen case a custom pulse stream is generated to meet the system needs. The PTO-QepDiv example demonstrates how the CLB can be used to generate a divided pulse stream from these eQEP inputs as shown in Figure 2-6. The divided pulse stream can then be sent to another device in the system. Both the QepDiv and PulseGen examples are documented in the *C2000 Position Manager PTO API Reference Guide*.

Figure 2-6. QepDIv Input and Output Diagram

### 2.5.3 Device List

- TMS320F2838xD/S

- TMS320F2837xD/S

- TMS320F2807x

- TMS320F28004x

- TMS320F28003x

- TMS320F28002x

### 2.5.4 Hardware Platforms and Software Examples

- Tamagawa T-Format Absolute-Encoder Master Interface Reference Design for C2000™ MCUs

- C2000 Position Manager PTO API Reference Guide

- MotorControl software development kit (SDK) for C2000 MCUs

- Position Manager BoosterPack (BOOSTXL-POSMGR)

- C2000<sup>™</sup> DesignDRIVE Development Kit for Industrial Motor Control (TMDXIDDK379D)

### 2.5.5 Documentation

- Training: How the C2000 Configurable Logic Block (CLB) tool integrates custom logic in my design

- CLB Tool User's Guide

- Designing With the C2000 Configurable Logic Block (CLB)

- How to Migrate Custom Logic From an FPGA/CPLD to C2000 Microcontrollers

- Fast Current Loop Library

### 2.6 Smart Sensing Across An Isolation Boundary

### 2.6.1 Value Proposition

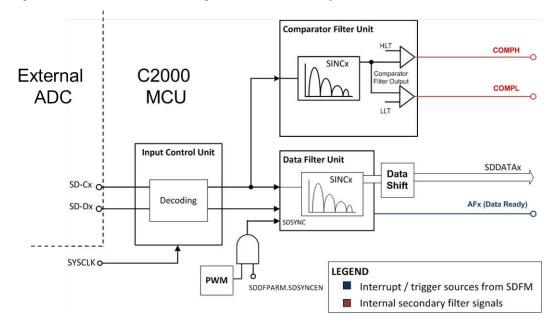

High voltage control systems often make use of a sigma-delta ADC in order to easily pass the analog information of the high voltage domain to the lower voltage domain where the MCU exists. Before the data stream can be used, it must be processed by a filter and demodulator. This logic exists on the C2000 MCU and is called the Sigma Delta Filter Module (SDFM) module. The high and low comparators inside the SDFM on a C2000 MCU can actuate the PWMs without CPU intervention saving valuable time to better control the system.

### 2.6.2 In Depth

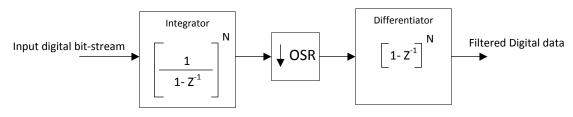

A sigma-delta type ADC is by design an over-sampling architecture. The ADC itself is a single bit design that over-samples the signal of interest to produce a higher order output. The modulation of this type of converter results in a binary output and, hence, a serial data stream. This serial data stream is then sent to the filter/ demodulator on the C2000 MCU for re-construction into a higher bit order digital representation of the sampled signal (Figure 2-7).

Figure 2-7. Filter and Demodulator Inside the C2000 SDFM

At this point an interrupt is generated to the MCU, informing the other domains there is new data to process and act upon.

The SDFM module on the C2000 MCU is unique in that not only can the converted data be read post filtering, but the PWMs can be switched based on this data automatically. Each SDFM module contains four channels. Inside each channel exists two filters: a primary filter that produces the SDFM data and a secondary filter containing both high and low limit comparators (Figure 2-8). This allows the system to control the PWM signals without waiting for CPU intervention, resulting in both lower latency as well as lower overall CPU utilization.

### Figure 2-8. SDFM Module With Both Primary and Secondary Filter Blocks on the TMS320F2837xD MCU

### 2.6.3 Device List

- TMS320F2838xD/S

- TMS320F2837xD/S

- TMS320F2807x

- TMS320F28004x

- TMS320F28003x

### 2.6.4 Hardware Platforms and Software Examples

- TMDSCNCD28388D controlCARD evaluation module

- LAUNCHXL-F28379D LaunchPad

- LAUNCHXL-F280049C LaunchPad

- TMDSCNCD280039C controlCARD evaluation module

- SDFM\_filter\_sync\_cpuread SW example for F2838xD/S

- SDFM\_pwm\_sync\_cpuread SW example for the F2838xD/S

## 2.6.5 Documentation

- TMS320F2838x Real-Time Microcontrollers Technical Reference Manual (for more information, see the SDFM chapter)

- TMS320F2837xD Real-Time Microcontrollers Technical Reference Manual (for more information, see the SDFM chapter)

- TMS320F28004x Real-Time Microcontrollers Technical Reference Manual (for more information, see the SDFM chapter)

- TMS320F28003x Real-Time Microcontrollers Technical Reference Manual (for more information, see the SDFM chapter)

- Real-Time controllers get new connectivity capabilities

## 2.7 Enabling Intra-Period Updates in High Bandwidth Control Topologies

### 2.7.1 Value Proposition

One of the most important considerations in designing a real-time control system is what the minimum sample to output delay the system can achieve (Figure 2-9). From the basics of providing stable control of the real-time system to realizing increased system efficiency the on-chip ADCs inside every C2000 real-time microcontroller are designed to minimize their effective time delay to the system in a variety of ways. Looking beyond the basics of a discrete ADCs and comparing to the C2000 on-chip ADCs there are differentiated features as a result of decades of involvement in real-time control.

Figure 2-9. Real-Time Signal Chain

### 2.7.2 In Depth

While choosing a discrete ADC for a system many factors are considered: raw converter speed, DC error terms like gain and offset, and AC error terms like SNR, THD(Shown in: Section 2.1). Beyond those parameters are the aspects of system integration, conversion speed with respect to the control loop, and sampling capability that can make or break a real-time control design.

**System integration:** One advantage of an integrated ADC is the lack of an external communications bus that adds complexity to the system in both latency of the comms channel but also noise considerations for bus routing. Once the ADC conversion is complete, minimizing the delay into the control scheme of the system is vital. The ADC results are accessible by all CPU cores, CLA cores, as well as DMAs.

Another common delay is introduced due to the latency introduced when the CPU is notified that the ADC conversion is complete. The C2000 ADCs implement a selectable early interrupt that takes advantage of the time the ADC incurs between the start of a sample and the completion of the analog to digital conversion. Since the ADC is integrated the C2000 MCU has the ability to sychronize to either the end of the analog sampling phase or the full conversion complete. This allows the C28x CPU or CLA to continue to do other tasks or calculations in parallel to the ADC conversion and use the ADC conversion as soon as it is available. Not only are wasted cylces minimized, but results in a more stable system control as the converted value used by the CPU is closer in time to the real world signal state.

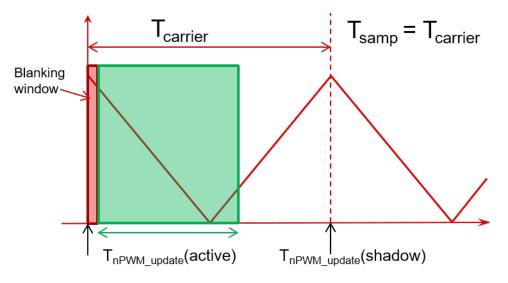

**Conversion Speed:**One aspect that is common in the evaluation of any ADC, discrete or integrated, is its conversion speed. This is how long it takes the ADC to convert the sampled analog signal into a digital representation. This is especially important in high bandwidth systems as it is beneficial to update the system intracycle vs waiting for the next full cycle of the control loop to happen (Figure 2-10). This is shown the (Fast Current Loop examples). The ADC on the C2000 MCU is capable of generating a conversion in as little as 260ns after the sample completes. This allows enough time for the C28x or CLA core to calculate the new PWM frequencies well ahead of the next control loop period allowing for the intra-cycle update to happen. The ePWM module plays a role here as well, allowing the PWM to be updated by writing to the active registers vs the shadow resigster, which would pend the update until the next full period.

Figure 2-10. Intra-Period Update of PWM

**Simultaneous sampling:** Each C2000 device referenced in this guide has at least 2 if not more ADCs. Looking at common real-time control topologies this allows simultaneous sampling of the motor currents. For the case of a system that uses a resolver for posistion sensing this would allow both the sine and cosine feedbacks to be sampled at the same point in time. Table 2-4 shows the potential effect on the system if such inputs are not sampled at the same point in time

| Control Loop Frequency | Phase Error With 500ns Sample Lag | Phase Error With 1µs Sample Lag |

|------------------------|-----------------------------------|---------------------------------|

| 10 kHz                 | 1.8 degrees                       | 3.6 degrees                     |

| 20 kHz                 | 3.6 degrees                       | 7.2 degrees                     |

| 50 kHz                 | 8.9 degrees                       | 17.8 degrees                    |

### Table 2-4. Potential Phase Error Caused by Sample Delay

### 2.7.3 Device List

- TMS320F2838xD/S

- TMS320F2837xD/S

- TMS320F2807x

- TMS320F28004x

- TMS320F28003x

- TMS320F28002x

- TMS320F280013x

- TMS320F280015x

TMS320F280015x

### 2.7.4 Hardware Platforms and Software Examples

- TIDM-02007 Dual-axis motor drive using fast current loop (FCL) and SFRA on a single MCU reference design

- BOOSTXL-3PHGANINV 48-V Three-Phase Inverter With Shunt-Based In-Line Motor Phase Current Sensing Evaluation Module

- BOOSTXL-3PHGANINV examples in C2000Ware Motor Control SDK

- TMDXIDDK379D C2000 DesignDRIVE Development Kit for Industrial Motor Control

### 2.7.5 Documentation

- Performance Analysis of Fast Current Loop (FCL) in Servo

- Quick Response Control of PMSM Using Fast Current Loop

# 2.8 Accurate Monitoring of Real-Time Control System Events Without the Need for Signal Conditioning

### 2.8.1 Value Proposition

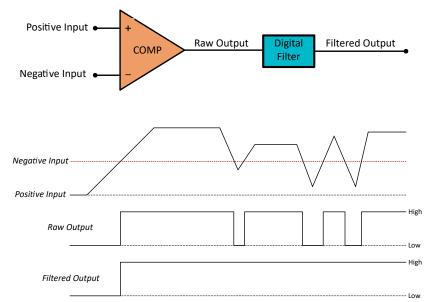

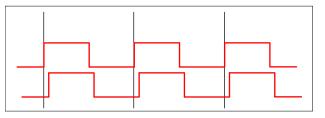

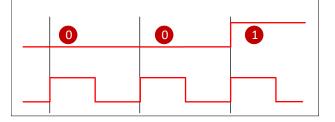

As mentioned in Section 4.4, quick detection of over-shoots and under-shoots is critical to the operation of a real-time control systems. However in reality, the transients of concern often have coupled noise, which can cause false trips and shut downs resulting in reliability issues in system functionality.

One approach typically used to remedy this is external passive RC filters to remove the high frequency noise from the signal of interest. This has drawbacks of BOM cost, PCB space, and slowing down the signal of interest. The CMPSS module on the C2000 MCU has configurable filters integrated in the device to filter out noise events without the need for an external RC filter.

### 2.8.2 In Depth

The CMPSS filter works on a principle of majority vote. It captures a window of high/low trip events from the comparator and sets the output to high or low depending on the threshold setting. The number of trip events captured by the window and the threshold setting used to determine the output are both configurable. Due to the configurability, the application can trade-off between how much noise to reject and how much the final trip is delayed. Figure 2-11 is a high level illustration of the filter in work. For further details, please refer to the CMPSS chapter in the TRM.

Figure 2-11. CMPSS Raw vs Filtered Output

### 2.8.3 Device List

- TMS320F2838xD/S

- TMS320F2837xD/S

- TMS320F2807x

- TMS320F28004x

- TMS320F28003x

- TMS320F28002x

- TMS320F280013x

TMS320F280015x

### 2.8.4 Hardware Platforms and Software Examples

- TMDSCNCDF28388D

- TMDSCNCDF28379D

- TMDSCNCDF280049C

- TMDSCNCD280039C

- TMDSCNCD280025

- TMDSCNCD2800137

- TMDSCNCD2800157

- F2838xD CMPSS Digital Filter SW Example

- F2837xD CMPSS Digital FilterSW Example

- F28004x CMPSS Digital Filter SW Example

- F28003x CMPSS Digital Filter SW Example

- F28002x CMPSS Digital Filter SW Example

- F280013x CMPSS Digital Filter SW Example

- F280015x CMPSS Digital Filter SW Example

### 2.8.5 Documentation

- TMS320F2838x Real-Time Microcontrollers Technical Reference Manual (for more information, see the CMPSS chapter)

- TMS320F2837xD Real-Time Microcontrollers Technical Reference Manual (for more information, see the CMPSS chapter)

- TMS320F28004x Real-Time Microcontrollers Technical Reference Manual (for more information, see the CMPSS chapter)

- TMS320F28003x Real-Time Microcontrollers Technical Reference Manual (for more information, see the CMPSS chapter)

- TMS320F28002x Real-Time Microcontrollers Technical Reference Manual (for more information, see the CMPSS chapter)

- TMS320F280013x Real-Time Microcontrollers Technical Reference Manual (for more information, see the CMPSS chapter)

- TMS320F280015x Real-Time Microcontrollers Technical Reference Manual (for more information, see the CMPSS chapter)

## **3 Processing Key Technologies**

### 3.1 Accelerated Trigonometric Math Functions

### 3.1.1 Value Proposition

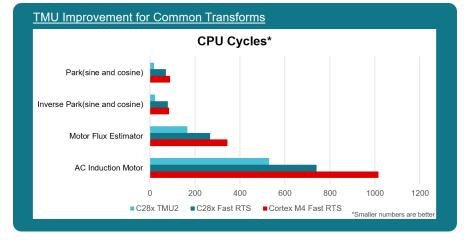

Trigonometric functions are used heavily in real-time control systems, both in power applications as well as motor control. Park Transforms (Figure 3-1), Space Vector Generation, and resolver angle are a few of these examples that rely on trigonometric math. The Trigonometric Math Unit (TMU) on C2000 MCUs enables an extended instruction set targeted at 32-bit floating-point trigonometry based calculations. This results both faster performance and smaller code size for Trigonometric functions.

|      | id |   | $\cos(\theta)$                    | $\sin(\theta)$ | 0   | $[i_{\alpha}]$ |

|------|----|---|-----------------------------------|----------------|-----|----------------|

| Park | i, | Ŧ | $\cos(\theta)$<br>$-\sin(\theta)$ | $\cos(\theta)$ | 0 X | iß             |

|      | i, |   | 0                                 | 0              | 1   | i,             |

### Figure 3-1. Park Transform

### 3.1.2 In Depth

Many common mathematical techniques in real-time control rely on the use of trigonometric functions: sine, cosine, and arc tangent are all examples. The TMU adds dedicated instructions to the C28x core for these functions as well as their inverse, that supersede the standard C library calls. As shown in Figure 3-2, significant cycle count reductions are possible using the TMU based instructions vs their Fast RTS counterparts.

There is also single instruction support for both square root as well as floating point division. These are often used in conjunction with the trigonometric functions previously listed. A full list of supported instructions and their cycle counts can be seen in Table 3-1. These instructions are inserted automatically by the C compiler on devices that have a TMU.

| Operation                            | C Equivalent Operation                        | C28x Pipeline Cycles            |

|--------------------------------------|-----------------------------------------------|---------------------------------|

| Multiply by 2*pi                     | a = b * 2pi                                   | 2 cycles + Sine/Cosine function |

| Divide by 2*pi                       | a = b / 2pi                                   | 2 cycles + Sine/Cosine function |

| Divide                               | a = b / c                                     | 5 cycles                        |

| Square Root                          | a = sqrt(b)                                   | 5 cycles                        |

| Sin Per Unit                         | a = sin(b*2pi)                                | 4 cycles                        |

| Cos Per Unit                         | a = cos(b*2pi)                                | 4 cycles                        |

| Arc Tangent Per Unit                 | a = atan(b)/2pi                               | 4 cycles                        |

| Arc Tangent 2 and Quadrant Operation | Operation to assist in calculating<br>ATANPU2 | 5 cycles                        |

| Table 3-1. This Supported instructions Summary | Table 3-1 | <b>U</b> Supporte | d Instructions Summary |

|------------------------------------------------|-----------|-------------------|------------------------|

|------------------------------------------------|-----------|-------------------|------------------------|

### Note

While the C2000 MCUs listed below all have a TMU module, the C compiler used to generate the target code must have the correct options selected to utilize this hardware. This is controlled in the Processor Options of the C2000 Compiler via the TMU support drop down, as well as using the "relaxed" setting for the floating point mode under C2000 Compiler  $\rightarrow$  Optimizations. Specific TMU based functions can be called explicitly as inline functions in the C source if that is preferable to a global setting.

### 3.1.3 Device List

- TMS320F2838xD/S

- TMS320F2837xD/S

- TMS320F2807x

- TMS320F28004x

- TMS320F28003x

- TMS320F28002x

- TMS320F280013x

- TMS320F280015x

### 3.1.4 Hardware Platforms and Software Examples

- TIDM-1007 Interleaved CCM Totem Pole Bridgeless Power Factor Correction (PFC) Reference Design

- TIDM-HV-1PH-DCAC Single-Phase Inverter Reference Design With Voltage Source and Grid Connected Modes

- TMDXIDDK379D C2000 DesignDRIVE Development Kit for Industrial Motor Control

- TMDSHVMTRINSPIN High Voltage Motor Control Kit with InstaSPIN-FOC and InstaSPIN-MOTION enabled for F280049C device lab7 and lab8

### 3.1.5 Documentation

- Enhancing the Performance Capabilities of the C2000™ MCU Family

- Signal Chain Benchmarking A Demonstration of Optimized Real-time Performance of C2000™ MCU

- TMS320C28x Extended Instruction Sets Technical Reference Manual

## 3.2 Fast Onboard Integer Division

### 3.2.1 Value Proposition

Compared to other standard arithmetic operations, accurate integer division are typically more complex and have much higher cycles counts in a MCU. Additionally in control algorithms, there is need for more linear division operations, such as Euclidean and Modulus that often consume additional CPU overhead. The FID module addresses this by supporting these special division definitions through dedicated HW, which enables control algorithms without the typical additional overhead associated with these methods. Finally, the FID supports various size and signed operands with optimum cycle counts.

### 3.2.2 In Depth

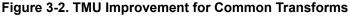

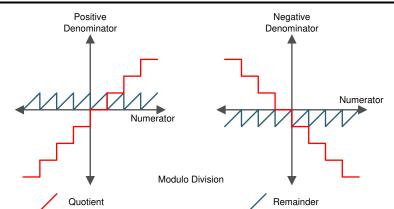

There are multiple definitions for division and modulo operations according to the programming language and computer science literature, each of these definitions provide different mathematical properties that can be beneficially employed in the application context. Truncated division is the standard division definition widely used in many programming languages like C. In this definition, the remainder will always have the sign of numerator. The transfer function of truncated division is shown in Figure 3-3, as can be observed that the function is non-periodic since there is a "platform" around zero point.

Figure 3-3. Truncated Division Function

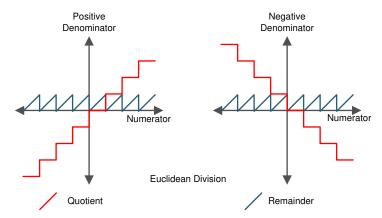

Due to the non-linearity around zero point, the function is not preferred in control applications. Thus nonconventional definitions of division and modulo operations are sometimes preferred for better linearity and periodicity. The transfer function of Floored/Modulo (Figure 3-4) and Euclidean division (Figure 3-5) functions are shown below. In the modulo division function the remainder will always have the sign of denominator, thus the function is linear around the zero point. In the Euclidean division, the remainder is always positive so the division function is linear around zero point and also the modulo function is periodic.

### Figure 3-4. Floored Division Function

Figure 3-5. Euclidean Division Function

The C28x CPU has added specialized instructions to enable applications to implement the above division and modulo definitions efficiently in hardware. These new instructions used to enable integer division are interruptible, have very low latency and support different types of operations (ui32/ui32, i32/ui32, i64/i32, ui64/ui32, ui64/ui32, ui64/ui64, i64/i64, and so forth). The cycles count for the different types of division operations and sizes of the operands achieved using Fast Integer Division unit are listed in and are also compared with the cycles without FID module in Table 3-2. As evident from the table, the FID unit provides several folds improvement in performance for different types of division operations which helps in minimizing the latency of control loop calculations.

| Division Operation  | Using C Operator '/' Without<br>FASTINTDIV Hardware on C28x | Using Intrinsics With<br>FASTINTDIV Hardware + C28x | Improvement Factor |

|---------------------|-------------------------------------------------------------|-----------------------------------------------------|--------------------|

| i16/i16 traditional | 52                                                          | 16                                                  | 3.3                |

| i16/i16 Euclidean   | 56                                                          | 14                                                  | 4.0                |

| i16/i16 Modulo      | 56                                                          | 14                                                  | 4.0                |