# Understanding and Interpreting Standard-Logic Data Sheets

Stephen M.Nolan, Jose M. Soltero, Shreyas Rao

#### **ABSTRACT**

Texas Instruments (TI) standard-logic product data sheets include descriptions of functionality and electrical specifications for the devices. Each specification includes acronyms, numerical limits, and test conditions that may be foreign to the user. The proper understanding and interpretation of the direct, and sometimes implied, meanings of these specifications are essential to correct product selection and associated circuit design. This application report explains each data sheet parameter in detail, how it affects the device, and how it impacts the application. This will enable component and system-design engineers to derive the maximum benefit from TI logic devices.

#### Contents

| 1 | Applic | ation Note Outline                   | , 2 |

|---|--------|--------------------------------------|-----|

| 2 | Introd | uction                               | . 2 |

| 3 | Top-L  | evel Look at the TI Logic Data Sheet | . 3 |

|   | 3.1    | Device Summary                       | . 4 |

|   | 3.2    | Pin Configuration and Functions      | 6   |

|   | 3.3    | Absolute Maximum Ratings             | 6   |

|   | 3.4    | ESD Ratings                          | . 7 |

|   | 3.5    | Recommended Operating Conditions     | . 8 |

|   | 3.6    | Electrical Characteristics           | . 8 |

|   | 3.7    | Live-Insertion Specifications        | . 9 |

|   | 3.8    | Timing Requirements                  | 10  |

|   | 3.9    | Switching Characteristics            | 10  |

|   | 3.10   | Noise Characteristics                | 11  |

|   | 3.11   | Operating Characteristics            | 11  |

|   | 3.12   | Parameter Measurement Information    | 12  |

| 4 | Disse  | cting the TI Logic Data Sheet        | 14  |

|   | 4.1    | Summary Device Description           | 14  |

|   | 4.2    | Revision History                     | 24  |

|   | 4.3    | Pin Configuration And Functions      | 24  |

|   | 4.4    | Absolute Maximum Ratings             | 24  |

|   | 4.5    | Recommended Operating Conditions     | 27  |

|   | 4.6    | Electrical Characteristics           | 35  |

|   | 4.7    | Live-Insertion Specifications        | 47  |

|   | 4.8    | Timing Requirements                  | 47  |

|   | 4.9    | Switching Characteristics            | 50  |

|   | 4.10   | Noise Characteristics                | 54  |

|   | 4.11   | Operating Characteristics            | 55  |

|   | 4.12   | Parameter Measurement Information    | 56  |

| 5 | Logic  | Compatibility                        | 56  |

| 6 | Detail | ed Description                       | 57  |

| 7 | Applic | ation and Implementation             | 57  |

| 8 | Power  | Supply Recommendations               | 58  |

| 9 | Layou  | t                                    | 58  |

Application Note Outline www.ti.com

| 10 | Conclusion      | 58 |

|----|-----------------|----|

| 11 | Acknowledgments | 58 |

| 12 | References      | 58 |

#### 1 Application Note Outline

This application report is organized into five main sections:

- 1. Introduction

- 2. Top-Level Look at the TI Logic Data Sheet. Overall layout and component parts of a data sheet are explained.

- Dissecting the TI Logic Data Sheet. JEDEC definition, the TI definition, an explanation, and, where

possible, helpful hints are presented for each specification term commonly found in TI logic data

sheets.

- 4. Logic Compatibility. Information in TI logic data sheets for determining the interface compatibility between different logic families is explained.

- 5. End matter, including the *Conclusion*, *Acknowledgments*, and *References* sections.

#### 2 Introduction

This application report is a synopsis of the information available from a typical TI data sheet with the purpose of assisting component and system-design engineers in selecting Texas Instruments (TI) standard-logic products. Information includes a brief description of terms, definitions, and testing procedures currently used for commercial, automotive and military specifications. Symbols, terms, and definitions generally are in accordance with those currently agreed upon by the JEDEC Solid State Technology Association for use in the USA and by the International Electrotechnical Commission (IEC) for international use.

#### 3 Top-Level Look at the TI Logic Data Sheet

The TI logic data sheet presents pertinent technical information for a particular device and is organized for quick access. This application report dissects a typical TI logic data sheet and describes the organization of all data sheets.

Typically, there are ten sections in TI-logic data sheets:

- 1. Front Page

- (a) Features

- (b) Applications

- (c) Description

- (d) Device Information Table

- (e) Front-Page Graphic(s)

- 2. Table of Contents

- 3. Revision History

- 4. Pin Configuration and Functions

- 5. Specifications

- (a) Absolute Maximum Ratings

- (b) ESD Ratings

- (c) Recommended Operating Conditions

- (d) Thermal Information

- (e) Electrical Characteristics

- (f) Timing Requirements

- (g) Switching Characteristics

- (h) Typical Characteristics

- 6. Parameter Measurement Information

- 7. Detailed Description

- (a) Overview

- (b) Functional Block Diagram

- (c) Feature Description

- (d) Device Functional Modes

- 8. Application and Implementation

- (a) Application Information

- (b) Typical Application

- (c) Design Requirements

- (d) Detailed Design Procedure

- (e) Application Curves

- 9. Power Supply Recommendations

- 10. Layout

- (a) Layout Guidelines

- (b) Layout Example

- 11. Device and Documentation Support

- 12. Mechanical, Packaging, and Ordering Information

#### 3.1 Device Summary

The first page of a data sheet contains all of the general information about a device (see Figure 1). This information includes:

1. Title, literature number, and dates of origination and revision, as applicable. Also, the top navigation contains hyperlinks leading directly to Product Folder, Sample & Buy, Technical Documents (related to the device), Tools & Software, and Support & Community.

SN74LVC1G08

SCES217Y - APRIL 1999-REVISED APRIL 2014

## SN74LVC1G08 Single 2-Input Positive-AND Gate

#### Figure 1. Example of Device Summary

2. The *Features* section identifies the main features and benefits of the device. This section includes features in a bulleted form. Figure 2 shows an example of the bulleted features.

#### 1 Features

- Available in the Ultra Small 0.64-mm<sup>2</sup> Package (DPW) With 0.5-mm Pitch

- Supports 5-V V<sub>CC</sub> Operation

- Inputs Accept Voltages to 5.5 V

- Provides Down Translation to V<sub>CC</sub>

- Max t<sub>pd</sub> of 3.6 ns at 3.3 V

- Low Power Consumption, 10-µA Max I<sub>CC</sub>

- ±24-mA Output Drive at 3.3 V

- I<sub>off</sub> Supports Live Insertion, Partial-Power-Down Mode, and Back Drive Protection

- Latch-Up Performance Exceeds 100 mA Per JESD 78, Class II

- ESD Protection Exceeds JESD 22

- 2000-V Human-Body Model (A114-A)

- 200-V Machine Model (A115-A)

- 1000-V Charged-Device Model (C101)

#### Figure 2. Feature Bullets

3. The *Applications* section for the device identifies the application scenarios for the device. Figure 3 shows an example of typical applications.

## 2 Applications

- ATCA Solutions

- · Active Noise Cancellation (ANC)

- Barcode Scanner

- Blood Pressure Monitor

- · CPAP Machine

- Cable Solutions

Figure 3. Typical Applications

4. The Description section provides a brief description of the device and its functionality

# 3 Description

This single 2-input positive-AND gate is designed for 1.65-V to 5.5-V  $V_{CC}$  operation.

The SN74LVC1G08 device performs the Boolean function or  $Y = A \cdot B$  or  $Y = \overline{A} + \overline{B}$  in positive logic.

#### Figure 4. Brief Description of Device

5. Figure 5 shows a logic diagram. The device information defines the nominal size of the device in each of the available packages.

#### Device Information<sup>(1)</sup>

| DEVICE NAME | PACKAGE    | BODY SIZE      |

|-------------|------------|----------------|

|             | SOT-23 (5) | 2.9mm × 1.6mm  |

|             | SC70 (5)   | 2.0mm × 1.25mm |

| SN74LVC1G08 | X2SON (4)  | 0.8mm × 0.8mm  |

|             | SON (6)    | 1.45mm × 1.0mm |

|             | SON (6)    | 1.0mm × 1.0mm  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

Figure 5. Device Information

- 6. Product-development stage note at the bottom of the data sheet

- 7. Table of contents to list the contents and the link to the page numbers alongside it.

- 8. Revision history for the device mentioning the changes to the data sheet with the dates.

# 4 Revision History

Changes from Revision X (March 2014 to Revision Y

Figure 6. Revision History

## 3.2 Pin Configuration and Functions

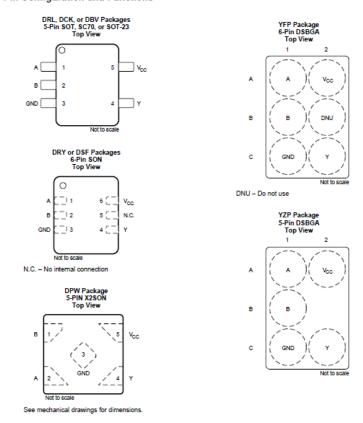

Figure 7 shows all the package options for the device. Figure 8 shows the functions of each pin sorted by the package list and their corresponding pin locations.

#### 5 Pin Configuration and Functions

Figure 7. Pin Configuration and Functions

#### Pin Functions PIN VO DESCRIPTION DRL, DCK, DPW DRY, DSF YZP NAME YFP DBV A1 Α1 Input A 2 Input B 1 2 В1 В1 DNU **B**2 Do not use GND 3 3 3 C1 C1 N.C. 5 No internal connection Vcc 5 5 6 A2 Α2 Power Pin 4 4 4 C2 C2 0 Output Y

Figure 8. Pin Functions Table

#### 3.3 Absolute Maximum Ratings

The Absolute Maximum Ratings section (Figure 9) specifies the stress levels that, if exceeded, may cause permanent damage to the device. However, these are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Also, exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

As Figure 9 indicates, there are two absolute maximums that may be exceeded under certain conditions. The input and output voltage ratings,  $V_I$  and  $V_O$ , may be exceeded if the input and output maximum clamp-current ratings,  $I_{IK}$  and  $I_{OK}$ , are observed.

#### 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                                                          |                           | MIN  | MAX  | UNIT |

|------------------|--------------------------------------------------------------------------|---------------------------|------|------|------|

| $V_{CC}$         | Supply voltage range                                                     |                           | -0.5 | 6.5  | V    |

| $V_{I}$          | Input voltage range <sup>(2)</sup>                                       |                           | -0.5 | 6.5  | V    |

| Vo               | Voltage range applied to any output in the high-impedan                  | ce or power-off state (2) | -0.5 | 6.5  | V    |

| Vo               | Voltage range applied to any output in the high or low state $^{(2)(3)}$ |                           |      |      | V    |

| I <sub>IK</sub>  | Input clamp current                                                      | V <sub>I</sub> < 0        |      | -50  | mA   |

| I <sub>OK</sub>  | Output clamp current                                                     | V <sub>O</sub> < 0        |      | -50  | mA   |

| Io               | Continuous output current                                                |                           |      | ±50  | mA   |

|                  | Continuous current through V <sub>CC</sub> or GND                        |                           |      | ±100 | mA   |

| T <sub>stg</sub> | Storage temperature range                                                |                           | -65  | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Figure 9. Example of Absolute Maximum Ratings Section

#### Helpful Hint:

All currents are defined with respect to conventional current flow into the respective terminal of the integrated circuit. This means that any current that flows out of the respective terminal is considered to be a negative quantity.

All limits are given according to the absolute-magnitude convention, with a few exceptions. In this convention, maximum refers to the greater magnitude limit of a range of like-signed values; if the range includes both positive and negative values, both limit values are maximums. Minimum refers to the smaller magnitude limit of a range of like-signed values; if the range includes both positive and negative values, then the minimum is implicitly zero. The most common exceptions to the absolute magnitude convention are temperature and logic levels. In these levels, zero does not represent the least-possible quantity, so the algebraic convention is commonly accepted. In this case, maximum refers to the most-positive value.

## 3.4 ESD Ratings

The ESD Ratings section of the data sheet specifies the Electrostatic Discharge ratings for the device tested as per JEDEC (Joint Electron Device Engineering Council) standards.

Usually, HBM (Human Body Model) and CDM (Charged Device Model) spec is tabulated as per the qualification process. Machine Model (MM) is discontinued.

**ESD Ratings**

|             |               |                                                                     | VALUE | UNIT |

|-------------|---------------|---------------------------------------------------------------------|-------|------|

| V           | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | 2000  | V    |

| $V_{(ESD)}$ | discharge     | Charged device model (CDM), per JEDEC specification JESD22-C101 (2) | 1000  | , v  |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

Figure 10. Example of ESD Ratings Section

<sup>(2)</sup> The input negative-voltage and output voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

<sup>(3)</sup> The value of V<sub>CC</sub> is provided in the *Recommended Operating Conditions* table.

#### 3.5 Recommended Operating Conditions

The Recommended Operating Conditions section of the data sheet sets the conditions for which Texas Instruments specifies device operation (see Figure 11). These are the conditions that the application circuit should provide to the device in order for it to function as intended. The limits for items that appear in this section are used as test conditions for the limits that appear in the Electrical Characteristics, Timing Requirements, Switching Characteristics, and Operating Conditions sections.

Recommended Operating Conditions (see Note 4)

|                          |                                    |                 | SN54LVTI | H16646 | SN74LVTI | H16646 | UNIT |

|--------------------------|------------------------------------|-----------------|----------|--------|----------|--------|------|

|                          |                                    |                 | MIN      | MAX    | MIN      | MAX    | UNIT |

| V <sub>cc</sub>          | Supply voltage                     | 2.7             | 3.6      | 2.7    | 3.6      | V      |      |

| $V_{IH}$                 | High-level input voltage           |                 | 2        |        | 2        |        | V    |

| V <sub>IL</sub>          | Low-level input voltage            |                 |          | 0.8    |          | 0.8    | V    |

| V <sub>I</sub>           | Input voltage                      |                 |          | 5.5    |          | 5.5    | V    |

| I <sub>OH</sub>          | High-level output current          |                 |          | -24    |          | -32    | mA   |

| I <sub>OL</sub>          | Low-level output current           |                 |          | 48     |          | 64     | mA   |

| Δt/Δν                    | Input transition rise or fall rate | Outputs enabled |          | 10     |          | 10     | ns/V |

| $\Delta t/\Delta V_{CC}$ | Power-up ramp rate                 |                 | 200      |        | 200      |        | µs/V |

| T <sub>A</sub>           | Operating free-air temperature     |                 | -55      | 125    | -40      | 85     | °C   |

NOTE: All unused control inputs of the device must be held at V<sub>CC</sub> or GND to ensure proper device operation. Refer to the TI application report, *Implications of Slow or Floating CMOS Inputs*, literature number SCBA004.

Figure 11. Example Recommended Operating Conditions Section

#### 3.6 Electrical Characteristics

The *Electrical Characteristics* (over recommended free-air temperature range) table, also known in the industry as the DC table, provides the specified electrical characteristic limits of the device when tested under the conditions in the *Recommended Operating Conditions* table, as given specifically for each parameter (see Figure 12).

#### Helpful Hint:

Although some parameters, such as  $C_i$  and  $C_{io}$ , can be tested with an ac signal, sometimes the electrical characteristics table is called the DC section.

Electrical Characteristics (Over Recommended Operating Free-air Temperature Range (unless otherwise noted))

| DAI                                                                                                    | DAMETER          | TEST CONDITIONS                                                                  |                                     |                      | 4LVTH16 | 646       | SN7                  | LINUT   |            |      |  |

|--------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------|-------------------------------------|----------------------|---------|-----------|----------------------|---------|------------|------|--|

| PAI                                                                                                    | RAMETER          | IESI C                                                                           | ONDITIONS                           | MIN                  | TYP (4) | MAX       | MIN                  | TYP (4) | MAX        | UNIT |  |

| V <sub>IK</sub>                                                                                        |                  | $V_{CC} = 2.7 \text{ V},$                                                        | I <sub>I</sub> = -18 mA             |                      |         | -1.2      |                      |         | -1.2       | V    |  |

|                                                                                                        |                  | $V_{CC} = 2.7 \text{ V to } 3.6 \text{ V},$                                      | I <sub>OH</sub> = -100 μA           | V <sub>CC</sub> -0.2 | 2       |           | V <sub>CC</sub> -0.2 | 2       |            |      |  |

| V                                                                                                      |                  | $V_{CC} = 2.7 \text{ V},$                                                        | I <sub>OH</sub> = -8 mA             | 2.4                  |         |           | 2.4                  |         |            | V    |  |

| $V_{OH}$                                                                                               |                  | V <sub>CC</sub> = 3 V                                                            | I <sub>OH</sub> = -24 mA            | 2                    |         |           |                      |         |            | V    |  |

|                                                                                                        |                  | V <sub>CC</sub> = 3 V                                                            | I <sub>OH</sub> = -32 mA            |                      |         |           | 2                    |         |            |      |  |

|                                                                                                        |                  | V - 27V                                                                          | I <sub>OL</sub> = 100 μA            |                      |         | 0.2       |                      |         | 0.2        |      |  |

|                                                                                                        |                  | $V_{CC} = 2.7 \text{ V}$                                                         | I <sub>OL</sub> = 24 mA             |                      |         | 0.5       |                      |         | 0.5        |      |  |

| V                                                                                                      |                  |                                                                                  | I <sub>OL</sub> = 16 mA             |                      |         | 0.4       |                      |         | 0.4        | V    |  |

| $V_{OL}$                                                                                               |                  | V 2.V                                                                            | I <sub>OL</sub> = 32 mA             |                      |         | 0.5       |                      |         | 0.5        | V    |  |

|                                                                                                        |                  | $V_{CC} = 3 V$                                                                   | I <sub>OL</sub> = 48 mA             |                      |         | 0.55      |                      |         |            |      |  |

|                                                                                                        |                  |                                                                                  | I <sub>OL</sub> = 64 mA             |                      |         |           |                      |         | 0.55       |      |  |

|                                                                                                        | Control inputs   | $V_{CC} = 3.6 \text{ V},$                                                        | $V_I = V_{CC}$ or GND               |                      |         | ±1        |                      |         | ±1         |      |  |

|                                                                                                        | Control inputs   | $V_{CC} = 0 \text{ or } 3.6 \text{ V},$                                          | $V_1 = 5.5 \text{ V}$               |                      |         | 10        |                      |         | 10         |      |  |

| $I_1$                                                                                                  |                  | $V_{CC} = 3.6 \text{ V}$                                                         | V <sub>I</sub> = 5.5 V              |                      |         | 20        |                      |         | 20         | μΑ   |  |

|                                                                                                        | A or B ports (5) |                                                                                  | $V_I = V_{CC}$                      |                      |         | 1         |                      |         | 1          |      |  |

|                                                                                                        | (3)              |                                                                                  | $V_1 = 0$                           |                      |         | -5        |                      |         | <b>-</b> 5 |      |  |

| l <sub>off</sub>                                                                                       | 1                | $V_{CC} = 0 V$ ,                                                                 | $V_1$ or $V_0 = 0$ to 4.5 V         |                      |         |           |                      |         | ±100       | μΑ   |  |

|                                                                                                        |                  | V 2.V                                                                            | V <sub>I</sub> = 0.8 V              | 75                   |         |           | 75                   |         |            |      |  |

| I <sub>I(hold)</sub>                                                                                   | A or B ports     | $V_{CC} = 3 V$                                                                   | V <sub>I</sub> = 2 V                | -75                  |         |           | -75                  |         |            | μΑ   |  |

|                                                                                                        |                  | $V_{CC} = 3.6 \text{ V (6)},$                                                    | $V_1 = 0 \text{ to } 3.6 \text{ V}$ |                      |         |           |                      |         | ±500       |      |  |

| I <sub>OZPU</sub>                                                                                      |                  | $\frac{V_{CC}}{OE}$ = 0 to 1.5 V, $V_{O}$ = 0.5 $\frac{V_{CC}}{OE}$ = don't care | V to 3 V,                           |                      |         | ±100<br>* |                      |         | ±100       | μA   |  |

| I <sub>OZPD</sub>                                                                                      |                  | $\frac{V_{CC}}{OE}$ = 1.5 V to 0, $V_O$ = 0.5 $\frac{V_{CC}}{OE}$ = don't care   | V to 3 V,                           |                      |         | ±100<br>* |                      |         | ±100       | μΑ   |  |

|                                                                                                        |                  |                                                                                  | Outputs high                        |                      |         | 0.19      |                      |         | 0.19       |      |  |

| $I_{CC}$                                                                                               |                  | $V_{CC} = 3.6 \text{ V}, I_{O} = 0,$<br>$V_{I} = V_{CC} \text{ or GND}$          | Outputs low                         |                      | 5       |           | 5                    |         |            | mA   |  |

|                                                                                                        |                  | VI = VCC OF GIVE                                                                 | Outputs disabled                    |                      |         | 0.19      |                      |         | 0.19       |      |  |

| $\Delta I_{CC}$ (7) $V_{CC} = 3 \text{ V to } 3.6 \text{ V, One ir}$<br>Other inputs at $V_{CC}$ or GN |                  |                                                                                  |                                     |                      | 0.2     |           |                      | 0.2     | mA         |      |  |

| C <sub>i</sub>                                                                                         |                  | V <sub>I</sub> = 3 V or 0                                                        |                                     |                      | 4       |           |                      | 4       |            | pF   |  |

| C <sub>io</sub>                                                                                        |                  | $V_0 = 3 \text{ V or } 0$                                                        |                                     |                      | 10      |           |                      | 10      |            | pF   |  |

- (3) On products compliant to MIL-PRF-38535, this parameter is not production tested.

- (4) All typical values are at  $V_{CC}$  = 3.3 V,  $T_A$  = 25°C.

- (5) Unused pins at  $V_{CC}$  or GND

- (6) This is the bus-hold maximum dynamic current. It is the minimum overdrive current required to switch the input from one state to another.

- (7) This is the increase in supply current for each input that is at the specified TTL voltage level, rather than V<sub>CC</sub> or GND.

Figure 12. Example Electrical-Characteristics Section

#### 3.7 Live-Insertion Specifications

The *Live-Insertion* section of the data sheet provides information about the parameters needed for true live insertion. These parameters include  $I_{off}$ ,  $I_{OZPU}$ ,  $I_{OZPD}$ , and BIAS  $V_{CC}$  for precharging purposes. An example of a typical live-insertion section is shown in Figure 13.

| Live-insertion Specifications for B port Over Recommended Operating Free-air Tem | emperature Range |

|----------------------------------------------------------------------------------|------------------|

|----------------------------------------------------------------------------------|------------------|

| PARAMETER                               |                                              | TEST CONDITIONS                                    |                                                                   | MIN  | MAX  | UNIT |

|-----------------------------------------|----------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------|------|------|------|

| I <sub>off</sub>                        | $V_{CC} = 0$ ,                               | BIAS $V_{CC} = 0$ ,                                | $V_1$ or $V_0 = 0$ to 1.5 V                                       |      | 10   | μA   |

| I <sub>OZPU</sub>                       | $V_{CC} = 0 \text{ to } 1.5 \text{ V},$      | BIAS $V_{CC} = 0$ ,                                | $V_0 = 0.5 \text{ V to } 1.5 \text{ V}, \overline{\text{OE}} = 0$ |      | ±30  | μΑ   |

| I <sub>OZPD</sub>                       | $V_{CC} = 1.5 \text{ V to } 0,$              | BIAS $V_{CC} = 0$ ,                                | $V_0 = 0.5 \text{ V to } 1.5 \text{ V}, \overline{\text{OE}} = 0$ |      | ±30  | μA   |

| I <sub>cc</sub> (BIAS V <sub>cc</sub> ) | $V_{CC} = 0 \text{ to } 3.15 \text{ V}$      | BIAS $V_{CC} = 3.15 \text{ V to } 3.45 \text{ V}$  | $V_0$ (B port) = 0 to 1.5 V                                       |      | 5    | mA   |

| ICC (DIAG VCC)                          | $V_{CC} = 3.15 \text{ V to } 3.45 \text{ V}$ | $V_{CC} = 3.13 \text{ V to } 3.43 \text{ V},$      | v <sub>0</sub> (Б роп) = 0 to 1.5 v                               |      | 10   | μΑ   |

| Vo                                      | $V_{CC} = 0$ ,                               | BIAS $V_{CC} = 3.3 \text{ V}$ ,                    | I <sub>O</sub> = 0                                                | 0.95 | 1.05 | V    |

| Io                                      | $V_{CC} = 0$ ,                               | BIAS $V_{CC} = 3.15 \text{ V to } 3.45 \text{ V},$ | $V_O$ (B port) = 0.6 V                                            | -1   |      | μΑ   |

Figure 13. Example Live-Insertion Section

## 3.8 Timing Requirements

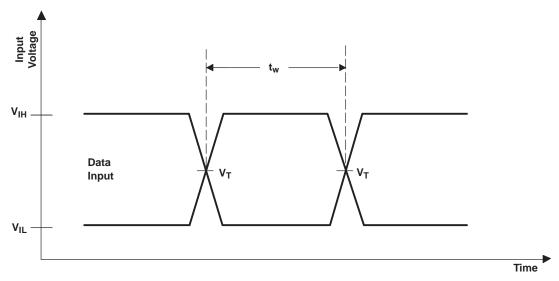

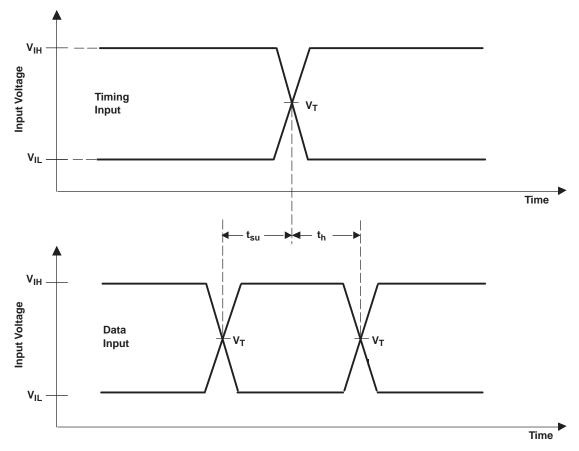

The *Timing Requirements* section of the data sheet is similar to the *Recommended Operating Conditions* section (see Figure 14). These are timings that the application circuit should provide to the device for it to function as intended. This section addresses the timing relationships between transitions of one or more input signals that are necessary to ensure device functionality and applies only to sequential-logic devices (for example, flip-flops, latches, and registers).

Timing Requirements (Over Recommended Operating Free-air Temperature Range (unless otherwise noted)) (see Figure 2)

|                    |                                 |           | S                            | N54LV | ГН16646             |       | S                            | N74LV | TH16646             |       |      |  |

|--------------------|---------------------------------|-----------|------------------------------|-------|---------------------|-------|------------------------------|-------|---------------------|-------|------|--|

|                    |                                 |           | V <sub>CC</sub> = 3<br>± 0.3 |       | V <sub>cc</sub> = 3 | 2.7 V | V <sub>cc</sub> = :<br>± 0.3 |       | V <sub>cc</sub> = 2 | 2.7 V | UNIT |  |

|                    |                                 |           | MIN                          | MAX   | MIN                 | MAX   | MIN                          | MAX   | MIN                 | MAX   |      |  |

| f <sub>clock</sub> | Clock frequency                 |           |                              | 150   |                     | 150   |                              | 150   |                     | 150   | MHz  |  |

| t <sub>w</sub>     | Pulse duration, CLK high or low |           | 3.3                          |       | 3.3                 |       | 3.3                          |       | 3.3                 |       | ns   |  |

| +                  | Setup time,                     | Data high | 1.2                          |       | 1.5                 |       | 1.2                          |       | 1.5                 |       | ns   |  |

| L <sub>su</sub>    | A or B before CLKAB↑ or CLKBA↑  | Data low  | 2                            |       | 2.8                 |       | 2                            |       | 2.8                 |       | 115  |  |

|                    | Hold time,                      | Data high | 0.5                          |       | 0                   |       | 0.5                          |       | 0                   |       | no   |  |

| t <sub>h</sub>     | A or B after CLKAB↑ or CLKBA↑   | Data low  | 0.5                          |       | 0.5                 |       | 0.5                          |       | 0.5                 |       | ns   |  |

Figure 14. Example Timing-Requirements Section

#### 3.9 Switching Characteristics

The Switching Characteristics section of the data sheet, also known in the industry as the AC table, includes the parameters that specify how fast the outputs will respond to signal changes at the inputs under specified conditions of supply voltage, temperature, and load (see Figure 15).

#### Helpful Hint:

The Switching Characteristics table is sometimes called the AC section, and should not be confused with the AC small-signal performance because switching characteristics describe the large-signal transient response of the circuit.

Switching Characteristics (Over recommended Operating Free-air Temperature Range,  $C_L = 50$  pF (unless otherwise noted)) (see Figure 2)

|                  |                | SN54LVTH16646    |     |     |                |                              |     |                     |       |     |                                 |     |                     |       |      |

|------------------|----------------|------------------|-----|-----|----------------|------------------------------|-----|---------------------|-------|-----|---------------------------------|-----|---------------------|-------|------|

| PARAMETER        | FROM           | FROM<br>(INPUT)  |     |     | TO<br>(OUTPUT) | V <sub>cc</sub> = 3<br>± 0.3 |     | V <sub>CC</sub> = 2 | 2.7 V |     | <sub>c</sub> = 3.3 \<br>± 0.3 V | 1   | V <sub>CC</sub> = 2 | 2.7 V | UNIT |

|                  | (*** ***)      | (001101)         | MIN | MAX | MIN            | MAX                          | MIN | TYP (8)             | MAX   | MIN | MAX                             |     |                     |       |      |

| f <sub>max</sub> |                |                  | 150 |     | 150            |                              | 150 |                     |       | 150 |                                 | MHz |                     |       |      |

| t <sub>PLH</sub> | CLKBA or       | A or B           | 1.3 | 4.5 |                | 5                            | 1.3 | 2.8                 | 4.2   |     | 4.7                             | 20  |                     |       |      |

| t <sub>PHL</sub> | CLKAB          | AUID             | 1.3 | 4.5 |                | 5                            | 1.3 | 2.8                 | 4.2   |     | 4.7                             | ns  |                     |       |      |

| t <sub>PLH</sub> | A or B         | B or A           | 1   | 3.6 |                | 4.1                          | 1   | 2.4                 | 3.4   |     | 3.9                             | ns  |                     |       |      |

| t <sub>PHL</sub> | AUIB           | BUIA             | 1   | 3.6 |                | 4.1                          | 1   | 2.1                 | 3.4   |     | 3.9                             | 115 |                     |       |      |

| t <sub>PLH</sub> | CDA or CAD (0) | Λ or D           | 1   | 4.7 |                | 5.6                          | 1   | 2.8                 | 4.5   |     | 5.4                             | 20  |                     |       |      |

| t <sub>PHL</sub> | SBA or SAB (9) | r SAB (9) A or B | 1   | 4.7 |                | 5.6                          | 1   | 3                   | 4.5   |     | 5.4                             | ns  |                     |       |      |

| t <sub>PZH</sub> | <u>OE</u>      | A or B           | 1   | 4.5 |                | 5.4                          | 1   | 2.5                 | 4.3   |     | 5.2                             | 20  |                     |       |      |

| t <sub>PZL</sub> | OE .           | AUID             | 1   | 4.5 |                | 5.4                          | 1   | 2.6                 | 4.3   |     | 5.2                             | ns  |                     |       |      |

| t <sub>PHZ</sub> | - OE           | A or B           | 2   | 5.8 |                | 6.3                          | 2   | 4                   | 5.6   |     | 6.1                             |     |                     |       |      |

| t <sub>PLZ</sub> | - OE           | AUID             | 2   | 5.6 |                | 6.3                          | 2   | 3.6                 | 5.4   |     | 6.1                             | ns  |                     |       |      |

| t <sub>PZH</sub> | DID            | A or D           | 1   | 4.6 |                | 5.5                          | 1   | 3                   | 4.4   |     | 5.3                             |     |                     |       |      |

| t <sub>PZL</sub> | DIR            | A or B           | 1   | 4.6 |                | 5.5                          | 1   | 3                   | 4.4   |     | 5.3                             | ns  |                     |       |      |

| t <sub>PHZ</sub> | DID            | A or D           | 1.5 | 6   |                | 7.1                          | 1.5 | 3.9                 | 5.7   |     | 6.8                             | 20  |                     |       |      |

| t <sub>PLZ</sub> | DIR            | A or B           | 1.5 | 5.5 |                | 6                            | 1.5 | 3.6                 | 5.2   |     | 5.7                             | ns  |                     |       |      |

<sup>(8)</sup> All typical values are at  $V_{CC} = 3.3 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

Figure 15. Example of Switching Characteristics Section

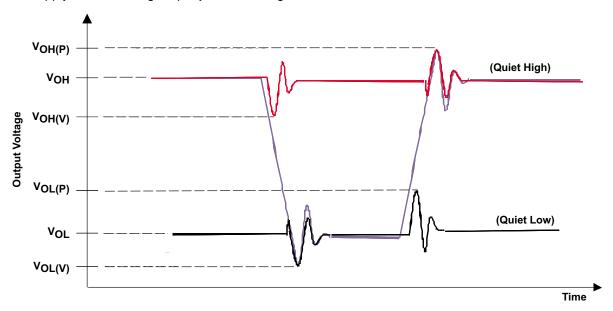

#### 3.10 Noise Characteristics

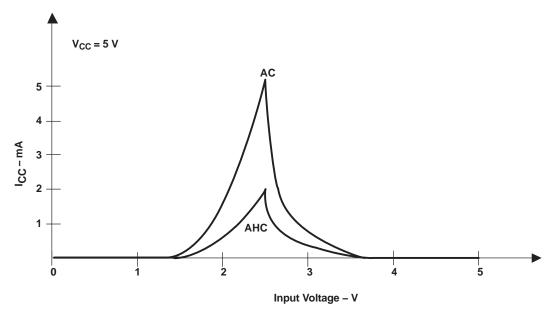

This section indicates a device's noise performance due to power-rail and ground-rail bounce associated with the high peak currents during dynamic switching (see Figure 16).

Noise Characteristics,  $V_{CC} = 5 \text{ V}$ ,  $C_L = 50 \text{ pF}$ ,  $T_A = 25^{\circ}\text{C}$  (see Note 4)

|             | PARAMETER                                     | SN74AHCT16541 |      | UNIT |      |

|-------------|-----------------------------------------------|---------------|------|------|------|

|             | FARAMETER                                     | MIN           | TYP  | MAX  | UNIT |

| $V_{OL(P)}$ | Quiet output, maximum dynamic V <sub>OL</sub> |               | 0.6  |      | ٧    |

| $V_{OL(V)}$ | Quiet output, minimum dynamic V <sub>OL</sub> |               | -0.3 |      | V    |

| $V_{OH(V)}$ | Quiet output, minimum dynamic V <sub>OH</sub> |               | 4.6  |      | V    |

| $V_{IH(D)}$ | High-level dynamic input voltage              | 2             |      |      | V    |

| $V_{IL(D)}$ | Low-level dynamic input voltage               |               |      | 8.0  | ٧    |

<sup>(10)</sup> Characteristics are for surface-mount packages only.

Figure 16. Example Noise-Characteristics Section

#### 3.11 Operating Characteristics

The Operating Characteristics section of the data sheet includes the parameter that specifies the power-dissipation capacitance ( $C_{pd}$ ) in a CMOS device (see Figure 17). For additional information on how  $C_{pd}$  is measured and used to calculate total CMOS-device power consumption in the application, refer to the TI application report, CMOS Power Consumption and  $C_{pd}$  Calculation, literature number SCAA035.

<sup>(9)</sup> These parameters are measured with the internal output state of the storage register opposite that of the bus input.

Operating Characteristics, T<sub>A</sub> = 25°C

|             | PARAMETER                              | TEST (      | CONDITIONS | V <sub>CC</sub> = 1.8 V | V <sub>CC</sub> = 2.5 V | $V_{CC} = 3.3 \text{ V}$ | UNIT |

|-------------|----------------------------------------|-------------|------------|-------------------------|-------------------------|--------------------------|------|

| FARAIVIETER |                                        |             | CHEITICHS  | TYP                     | TYP                     | TYP                      | ONT  |

| $C_{pd}$    | Power dissipation capacitance per gate | $C_L = 0$ , | f = 10 MHz | 20                      | 21                      | 23                       | pF   |

Figure 17. Example of Operating-Characteristics Section

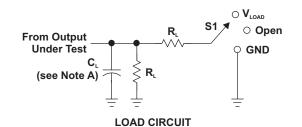

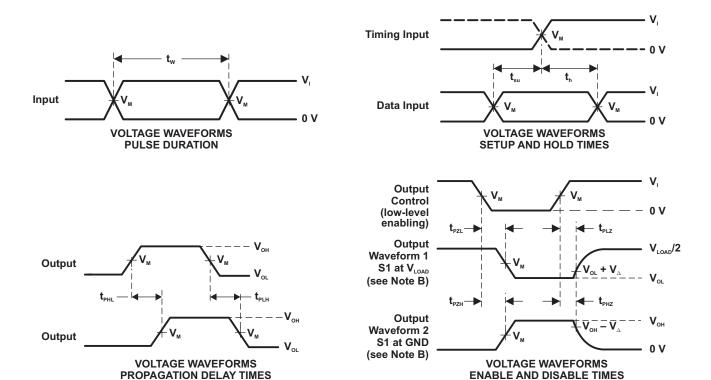

#### 3.12 Parameter Measurement Information

The *Parameter Measurement Information* section of the data sheet illustrates the test loads and waveforms that are used when testing the device (see Figure 18).

#### 8 Parameter Measurement Information

3.3 V ± 0.3 V

2.7 V

<2.5 ns

| TEST                                      | S1                       |  |  |  |  |

|-------------------------------------------|--------------------------|--|--|--|--|

| t <sub>pd</sub>                           | Open                     |  |  |  |  |

| $t_{_{\mathrm{PLZ}}}/t_{_{\mathrm{PZL}}}$ | <b>V</b> <sub>LOAD</sub> |  |  |  |  |

| t <sub>PHZ</sub> /t <sub>PZH</sub>        | GND                      |  |  |  |  |

| .,              | IN              | INPUTS                          |                    | .,                       |                |                | .,             |  |

|-----------------|-----------------|---------------------------------|--------------------|--------------------------|----------------|----------------|----------------|--|

| V <sub>cc</sub> | V,              | t <sub>r</sub> / t <sub>f</sub> | V <sub>M</sub>     | <b>V</b> <sub>LOAD</sub> | C <sup>r</sup> | R <sub>⊾</sub> | V <sub>∆</sub> |  |

| 1.8 V ±0.15 V   | V <sub>cc</sub> | <u>≤</u> 2 ns                   | V <sub>cc</sub> /2 | 2 × V <sub>cc</sub>      | 30 pF          | <b>1 k</b> Ω   | 0.15 V         |  |

| 2.5 V ± 0.2 V   | V <sub>cc</sub> | ≤2 ns                           | V <sub>cc</sub> /2 | 2 × V <sub>cc</sub>      | 30 pF          | $500\Omega$    | 0.15 V         |  |

| 2.7 V           | 2.7 V           | ≤2.5 ns                         | 1.5 V              | 6 V                      | 50 pF          | $500\Omega$    | 0.3 V          |  |

1.5 V

6 V

50 pF

$500\Omega$

0.3 V

NOTES: A. C. includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low, except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high, except when disabled by the output control.

- C. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$ 10 MHz,  $Z_{o}$  = 50  $\Omega$ .

- D. The outputs are measured one at a time, with one transition per measurement.

- E.  $t_{PLZ}$  and  $t_{PHZ}$  are the same as  $t_{dis}$ .

- F.  $t_{\mbox{\tiny PZL}}$  and  $t_{\mbox{\tiny PZH}}$  are the same as  $t_{\mbox{\tiny en}}.$

- G.  $t_{PLH}$  and  $t_{PHL}$  are the same as  $t_{pd}$ .

- H. All parameters and waveforms are not applicable to all devices.

Figure 18. Example Parameter Measurement Information Section

#### 4 Dissecting the TI Logic Data Sheet

In the following paragraphs, the TI logic data sheet is dissected, and every section and specification is explained in detail.

#### 4.1 Summary Device Description

#### 4.1.1 Title, Literature Number, and Dates of Origination and Revision

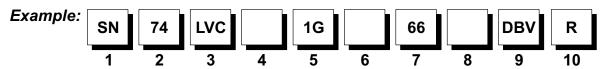

The device number and title appear at the top of every page. The device number is the number of the parent device. The fully qualified part number for a specific device can be found in the *Orderable Part Number* table. Figure 19 is a chart to help decode information in the TI logic-device part number.

The literature number is a unique identifier used by TI to identify, store and retrieve a data sheet in internal files.

The month and year of origination is the first date of publication of the data sheet. If a data sheet is modified, the revision date (month and year) is added. If there are multiple revisions, only the latest revision date appears.

#### Standard Prefix 1

SN - Standard Prefix Examples:

SNJ - Conforms to MIL-PRF-38535 (QML)

#### Temperature Range

Examples: 54 Military

74 - Commercial

#### 3 Family

Examples: Blank = Transistor-Transistor Logic (TTL) ABT - Advanced BiCMOS Technology

ABTE/ETL - Advanced BiCMOS Technology/

**Enhanced Transceiver Logic** AC/ACT - Advanced CMOS Logic

AHC/AHCT - Advanced High-Speed CMOS Logic

ALB - Advanced Low-Voltage BiCMOS ALS - Advanced Low-Power Schottky Logic

ALVC - Advanced Low-Voltage CMOS Technology

ALVT - Advanced Low-Voltage BiCMOS Technology

AS – Advanced Schottky Logic

AUC - Advanced Ultra Low-Voltage CMOS Logic

AVC - Advanced Very Low-Voltage CMOS Logic

BCT - BiCMOS Bus-Interface Technology

CBT - Crossbar Technology

CBTLV - Low-Voltage Crossbar Technology CD4000 – CMOS B-Series Integrated Circuits

F - F Logic

FB - Backplane Transceiver Logic/Futurebus+

FCT - Fast CMOS TTL Logic GTL – Gunning Transceiver Logic GTLP - Gunning Transceiver Logic Plus HC/HCT - High-Speed CMOS Logic HSTL - High-Speed Transceiver Logic LS - Low-Power Schottky Logic LV - Low-Voltage CMOS Technology LVC - Low-Voltage CMOS Technology

LVT - Low-Voltage BiCMOS Technology PCA/PCF – I<sup>2</sup>C Inter-Integrated Circuit Applications

S - Schottky Logic

SSTL/SSTV - Stub Series-Terminated Logic TVC - Translation Voltage Clamp Logic

VME – VERSAmodule Eurocard Bus Technology

#### Special Features

Blank = No Special Features Examples:

C – Configurable V<sub>CC</sub> (LVCC) D – Level-Shifting Diode (CBTD)

H – Bus Hold (ALVCH)

K – Undershoot-Protection Circuitry (CBTK) R – Damping Resistor on Inputs/Outputs (LVCR)

S – Schottky Clamping Diode (CBTS)

Z – Power-Up 3-State (LVCZ)

#### Bit Width

Examples: Blank = Gates, MSI, and Octals

1G - Single Gate 2G - Dual Gate

3G - Triple Gate

8 - Octal IEEE 1149.1 (JTAG) 16 – Widebus (16, 18, and 20 bit) 18 - Widebus IEEE 1149.1 (JTAG)

32 - Widebus+ □ (32 and 36 bit)

6 **Options**

Blank = No Options Examples:

2 - Series Damping Resistor on Outputs

4 - Level Shifter  $25 - 25-\Omega$  Line Driver

#### **Function**

244 Noninverting Buffer/Driver Examples:

374 - D-Type Flip-Flop

573 - D-Type Transparent Latch

640 - Inverting Transceiver

#### Device Revision

Examples: Blank = No Revision

Letter Designator A-Z

#### 9 **Packages**

Commercial: D, DW – Small-Outline Integrated Circuit (SOIC)

DB, DBQ, DCT, DL - Shrink Small-Outline Package

(SSOP)

DBB, DGV - Thin Very Small-Outline Package (TVSOP) DBQ - Quarter-Size Small-Outline Package (QSOP)

DBV, DCK, DCY, PK - Small-Outline Transistor (SOT) DCU - Very Thin Shrink Small-Outline Package (VSSOP)

DGG, PW - Thin Shrink Small-Outline Package (TSSOP)

FN - Plastic Leaded Chip Carrier (PLCC) GGM, GKE, GKF, ZKE, ZKF - MicroStar BGA□ Low-Profile Fine-Pitch Ball Grid Array (LFBGA)

GQL, GQN, ZQL, ZQN - MicroStar Jr.

Very-Thin-Profile Fine-Pitch Ball Grid Array (VFBGA)

N, NT, P - Plastic Dual-In-Line Package (PDIP) NS, PS - Small-Outline Package (SOP)

PAG, PAH, PCA, PCB, PM, PN, PZ - Thin Quad

Flatpack (TQFP)

PH, PQ, RC - Quad Flatpack (QFP) PZA - Low-Profile Quad Flatpack (LQFP) RGY - Quad Flatpack No Lead (QFN)

YEA, YZA - NanoStar and NanoFree □

Die-Size Ball Grid Array (DSBGA<sup>†</sup>)

– FK Leadless Ceramic Chip Carrier (LCCC) Military:

GB - Ceramic Pin Grid Array (CPGA)

HFP, HS, HT, HV - Ceramic Quad Flatpack (CQFP) J, JT – Ceramic Dual-In-Line Package (CDIP) W, WA, WD - Ceramic Flatpack (CFP)

#### 10 Tape and Reel

Devices in the DB and PW package types include the R designation for reeled product. Existing product inventory designated LE may remain, but all products are being converted to the R designation.

Old Nomenclature - SN74LVTxxxDBLE Examples:

New Nomenclature - SN74LVTxxxADBR

LE – Left Embossed (valid for DB and PW packages only) R – Standard (valid for all surface-mount packages)

There is no functional difference between LE and R designated products, with respect to the carrier tape, cover tape, or reels used.

† DSBGA is the JEDEC reference for wafer chip scale package (WCSP).

Figure 19. Device Number and Package Designators for TI Devices

Special features of TI standard logic devices are designated in the device number by abbreviations, as shown in the following list and defined in the following paragraphs.

- Blank No special features

- C Configurable V<sub>CC</sub>

- · D Level-shifting diode

- H Bus hold

- K Undershoot-protection circuitry

- R Damping resistor on inputs/outputs

- S Schottky clamping diode

- Z Power-up 3-state

#### 4.1.1.1 Configurable $V_{cc}$ (C)

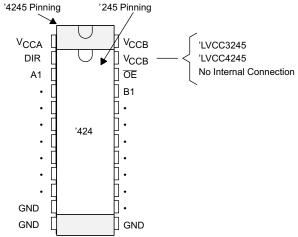

Configurable  $V_{CC}$  is a feature of devices that are designed as dual-supply level shifters, for example, SN74LVCC3245A and SN74LVCC4245A. Using these devices allows selection of the voltage to be applied to  $V_{CC}$  on the B-port side ( $V_{CCB}$ ) or A-port side ( $V_{CCA}$ ) (see Figure 20).

Copyright © 2016, Texas Instruments Incorporated

|               | V <sub>CCA</sub><br>A Port | V <sub>CCB</sub><br>B PORT | TRANSLATION<br>(BIDIRECTIONAL FLOW) |  |  |  |

|---------------|----------------------------|----------------------------|-------------------------------------|--|--|--|

| SN74LVCC3245A | 2.3 V-3.6 V                | 3 V-5.5 V                  | 2.5 V to 3.3 V or 3.3 V to 5 V      |  |  |  |

| SN74LVCC4245A | 5 V                        | 3 V-5 V                    | 5 V to 3.3 V                        |  |  |  |

Figure 20. Example of Configurable V<sub>cc</sub> Devices

Designers can use these devices in existing single-voltage systems. When systems become mixed-voltage systems, these devices do not need to be replaced, allowing for quicker time to market.

#### 4.1.1.2 Level-Shifting Diode (D)

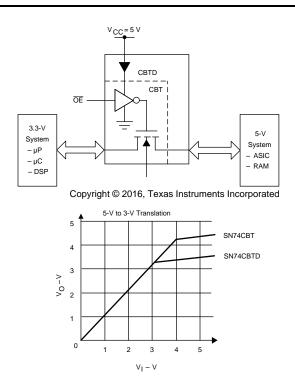

Devices with D as part of the device number have an integrated diode in the  $V_{\rm CC}$  line. Examples are crossbar switches SN74CBTD3306 (with the integrated diode) and SN74CBT3306 (without the integrated diode). These devices allow 5-V to 3.3-V translation if no drive is required. Bidirectional data transmission is allowed between 5-V TTL and 3.3-V LVTTL, whereas only unidirectional level translation is allowed from 5-V CMOS to 3.3-V LVTTL (see Figure 21). The integrated diode saves designers both board space and component cost.

Figure 21. CBT vs CBTD With Internal Diode

#### 4.1.1.3 Bus-Hold (H)

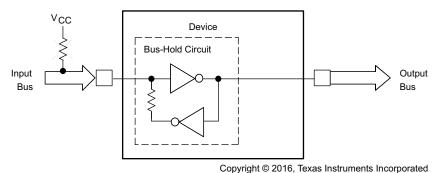

A bus-hold circuit is implemented in selected logic families to help solve the floating-input problem inherent in all CMOS inputs (refer to the application report, *Implications of Slow or Floating CMOS Inputs*, literature number SCBA004). The bus-hold circuit maintains the last known input state into the device and, as an additional benefit, pullup or pulldown resistors no longer are needed (see Figure 22). The advantages of devices with this circuit are board-space savings and reduced component costs.

Figure 22. Benefit of Using Bus-Hold Devices

#### 4.1.1.4 Damping Resistor on Inputs/Outputs (R)

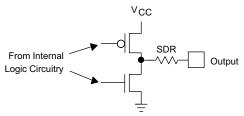

Series damping resistors (SDR), denoted by R in the device number, are included at all input/output and output ports of designated devices (see Figure 23). The SDRs limit the current, thereby reducing signal undershoot and overshoot noise. Additionally, SDRs make line termination easier, which improves signal quality by reducing ringing and line reflections.

Copyright © 2016, Texas Instruments Incorporated

Figure 23. Series-Damping-Resistor Option

#### 4.1.1.5 Schottky Clamping Diode (S)

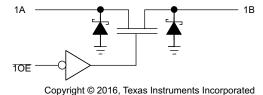

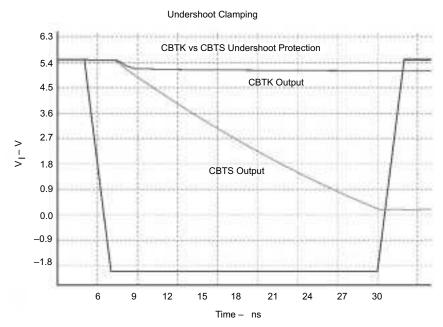

Schottky diodes are incorporated in inputs and outputs to clamp undershoot (see Figure 24). The Schottky diodes prevent undershoot signals from dropping below a specified level, reducing the possibility of damage to connected devices by large undershoots that can occur without the Schottky diodes.

Figure 24. Schottky Clamping-Diode Device Schematic

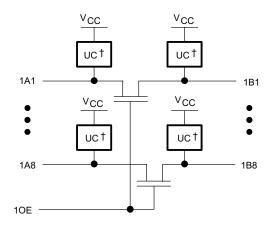

#### 4.1.1.6 Undershoot-Protection Circuitry (K)

TI undershoot-protection circuitry (UPC) functions similarly to Schottky clamping diodes, with one major difference. UPC is an active clamping structure. UPC can greatly reduce undershoot voltage, increasing protection from corrupted data (see Figure 25).

Figure 25. Undershoot-Proctection Circuity in K-Option Devices

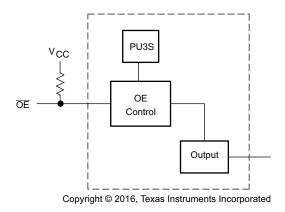

## 4.1.1.7 Power-Up 3-State (Z)

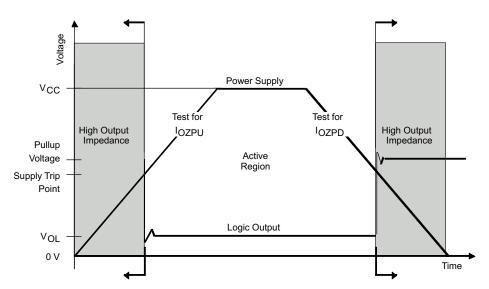

The power-up 3-state (PU3S) feature ensures valid output levels during power up and ensures the valid high-impedance state during power down. The output enable pin  $(\overline{OE})$  must be tied high (to  $V_{CC}$ ) through an external pullup resistor (see Figure 26). For more information, see  $I_{OZPD}$  and  $I_{OZPU}$  specifications in the *Electrical Characteristics* section.

Figure 26. PU3S Circuit Implementation

#### 4.1.2 Features Bullets

The Features section highlights information about the salient functions, features, and benefits of the device. Some features bullets provide an indication of functionality and application of the device, such as "Eight D-type Flip-Flops in a Single Package", "3-State Outputs", "Carry Output for N-bit Cascading" (for a binary counter), "Performs Parallel-to-Serial Conversion", or "Bidirectional Interface Between GTLP Signal Levels and LVTTL Logic Levels". Some data sheets contain electrostatic discharge (ESD) or latch-up test results and the associated JEDEC test conditions. The following are explanations of some common features bullets.

- Flow-Through Architecture Optimizes PCB Layout

- The data inputs and corresponding outputs are on opposite sides of the package. This feature makes

printed circuit board trace routing easier.

- Bus-Hold on Data Inputs Eliminates the Need for External Pullup/Pulldown Resistors

- Active bus-hold circuitry holds unused or non-driven inputs at a valid logic state. Use of pullup or

pulldown resistors with the bus-hold circuitry is not recommended. For more information on bus hold

refer to the TI application report, Bus-Hold Circuit, literature number SCLA015.

- I<sub>off</sub> Supports Partial-Power-Down Mode Operation

- This device is fully specified for partial-power-down applications using I<sub>off</sub>. The I<sub>off</sub> circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down.

- I<sub>off</sub> and Power-Up 3-State Support Hot Insertion

- This device is fully specified for hot-insertion applications using I<sub>off</sub> and power-up 3-state. The I<sub>off</sub> circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down. The power-up 3-state circuitry places the outputs in the high-impedance state during power up and power down, which prevents driver conflict.

- $\bullet$   $\,$   $\,$   $I_{\text{off}},$  Power-up 3-State, and BIAS  $V_{\text{CC}}$  Support Live Insertion

- This device is fully specified for live-insertion applications using I<sub>off</sub>, power-up 3-state, and BIAS V<sub>CC</sub>.

The I<sub>off</sub> circuitry disables the outputs, preventing damaging current backflow through the device when it is powered down. The power-up 3-state circuitry places the outputs in the high-impedance state during power up and power down, which prevents driver conflict. The BIAS V<sub>CC</sub> circuitry precharges and preconditions the input/output connections on a device port, preventing disturbance of active data on the bus during card insertion or removal and permits true live-insertion capability.

#### 4.1.3 Package Options and Pinouts

This section contains a top-view illustration of the leaded-package pinout(s) and a bottom view of certain nonleaded packages. Package dimensions and other package information is available in the *Mechanical Data* section of the *Semiconductor Group Packaging Outlines Reference Guide*, or *Analog and Logic packaging* literature number SSZB138A.

#### 4.1.4 Applications

The Applications section contains a list of the typical system applications the device can used in.

#### 4.1.5 Description

The *Description* section contains a written detailed explanation of the functionality and features of the device.

#### 4.1.6 BGA Packaging Top-View Illustrations and Pin-Assignments Table

This section contains the top-view illustrations and pin assignments for applicable BGA package types.

#### 4.1.7 Device Information

A table is provided that gives the fully qualified orderable part number and topside symbolization for every package option of the device.

TI has converted to an advanced order-entry system that provides significant improvements to all facets of TI business, from production, to order entry, to logistics. One requirement is a limitation of TI part numbers to no more than 18 characters. Based on customer inputs, TI determined that the least-disruptive implementations would be as outlined below:

#### 1. Package alias

DI R

**DGVR**

DGGR/DBBR

GKER/GKFR/GQLR

TI uses an alias to denote specific packages for device numbers that exceed 18 characters. Table 1 shows a mapping of package codes to an alias representation.

Current<br/>Package CodeAliasDLLDGG/DBBGDGVVGKE/GKF/GQLK

Table 1. Package Alias

#### 2. Resistor-option nomenclature

For device numbers of more than 18 characters and with input and output resistors, TI has adopted a simplified nomenclature to designate the resistor option. This eliminates the redundant "2" (designating output resistors) when the part number also contains an "R" (designating input/output resistors).

LR - tape/reel packing

GR - tape/reel packing

VR - tape/reel packing

KR - tape/reel packing

Input/Output Resistor

Output Resistor

Current: SN74 ALVCH R 16 2 245 A New: SN74 ALVCH R 16 245 A

There is no change to the device or data sheet electrical parameters. The packages involved and the changes in nomenclature are given in Table 1.

The approximate body size in millimeters are given for each of the package .

#### 4.1.8 Function Table

The function table illustrates the expected logic values on the outputs, when the inputs have the given stimuli applied.

The following symbols are used in function tables in TI data sheets:

H = high level (steady state)

L = low level (steady state)

↑ = transition from low to high level

↓ = transition from high to low level

= value/level or resulting value/level is routed to indicated destination

= value/level is re-entered

X = irrelevant (any input, including transitions)

Z = off (high-impedance) state of a 3-state output

a . . . h = the level of steady-state inputs A through H, respectively

Q<sub>0</sub> = level of Q before the indicated steady-state input conditions were established

$\overline{Q}_0$  = complement of  $Q_0$  or level of  $\overline{Q}$  before the indicated steady-state input

conditions were established

$Q_n$  = level of Q before the most-recent active transition indicated by  $\downarrow$  or  $\uparrow$

= one high-level pulse = one low-level pulse

Toggle = each output changes to the complement of its previous level on each active

transition indicated by ↓ or ↑

In the input columns, if a row contains only the symbols H, L, or X, the indicated output is valid when the input configuration is achieved, regardless of the sequence in which it is achieved. The output persists as long as the input configuration is maintained.

In the input columns, if a row contains H, L, and/or X, together with  $\uparrow$  and/or  $\downarrow$ , the output is valid when the input configuration is achieved, but the transition(s) must occur after steady-state levels are attained. If the output is shown as a level (H, L, Q<sub>0</sub>, or  $\overline{Q_0}$ ), it persists as long as the steady-state input levels and the levels that terminate indicated transitions are maintained. Unless otherwise indicated, input transitions in the opposite direction to those shown have no effect at the output. If the output is shown as a pulse, "-", or "- -", the pulse follows the indicated input transition and persists for an interval that is dependent on the circuit.

Among the most complex function tables are those of the shift registers. These embody most of the symbols used in any of the function tables, and more. Table 2 is the function table of a 4-bit bidirectional universal shift register.

**Table 2. Function Table**

| INPUTS |    |    |              |      |          |   |   |   | OUTPUTS |          |                   |                   |                   |

|--------|----|----|--------------|------|----------|---|---|---|---------|----------|-------------------|-------------------|-------------------|

| CLEAR  | MC | DE | CLOCK SERIAL |      | PARALLEL |   |   | 0 | 0       | 0        | 0                 |                   |                   |

| CLEAR  | S1 | S0 | CLOCK        | LEFT | RIGHT    | Α | В | С | D       | $Q_A$    | $Q_B$             | Q <sub>c</sub>    | $Q_{D}$           |

| L      | Χ  | Χ  | Х            | Х    | Х        | Х | Χ | Х | Χ       | L        | L                 | L                 | L                 |

| Н      | Χ  | Χ  | L            | Х    | Χ        | Χ | Χ | X | Χ       | $Q_{A0}$ | $Q_{B0}$          | $Q_{C0}$          | $Q_{D0}$          |

| Н      | Н  | Н  | <b>↑</b>     | Х    | Χ        | а | b | С | d       | а        | b                 | С                 | d                 |

| Н      | L  | Н  | <b>↑</b>     | Х    | Н        | Н | Н | Н | Н       | Н        | $\mathbf{Q}_{An}$ | $\mathbf{Q}_{Bn}$ | $\mathbf{Q}_{Cn}$ |

| Н      | L  | Н  | <b>↑</b>     | Х    | L        | L | L | L | L       | L        | $\mathbf{Q}_{An}$ | $\mathbf{Q}_{Bn}$ | $\mathbf{Q}_{Cn}$ |

| Н      | Н  | L  | <b>↑</b>     | Н    | X        | X | Χ | X | Χ       | $Q_{Bn}$ | $\mathbf{Q}_{Cn}$ | $\mathbf{Q}_{Dn}$ | Н                 |

| Н      | Н  | L  | <b>↑</b>     | L    | X        | X | Χ | X | Χ       | $Q_{Bn}$ | $\mathbf{Q}_{Cn}$ | $\mathbf{Q}_{Dn}$ | L                 |

| Н      | L  | L  | X            | X    | X        | Х | Χ | Χ | Χ       | $Q_{A0}$ | $Q_{B0}$          | $Q_{C0}$          | $Q_{D0}$          |

The first row of the table represents a synchronous clearing of the register and states that, if clear is low, all four outputs will be reset low, regardless of the other inputs, which are denoted by X. In the following rows, clear is inactive (high); therefore, it has no effect.

The second row shows that, as long as the clock input remains low (while clear is high), no other input has any effect, and the outputs maintain the levels they assumed before the steady-state combination of clear high and clock low was established. Because, on other rows of the table only the rising transition of the clock is shown to be active, the second row implicitly shows that no further change in the outputs occurs while the clock remains high or on the high-to-low transition of the clock.

The third row of the table represents synchronous parallel loading of the register and states that if S1 and S0 are both high, then, without regard to the serial input, the data entered at A is at output  $Q_A$ , data entered at B is at  $Q_B$ , and so forth, following a low-to-high clock transition.

The fourth and fifth rows represent the loading of high- and low-level data, respectively, from the shift-right serial input and the shifting of previously entered data one bit; data previously at  $Q_A$  is now at  $Q_B$ , the previous levels of  $Q_B$  and  $Q_C$  are now at  $Q_C$  and  $Q_D$ , respectively, and the data previously at  $Q_D$  no longer is in the register. This entry of serial data and shift takes place on the low-to-high transition of the clock when S1 is low and S0 is high, and the levels at inputs A through D have no effect.

The sixth and seventh rows represent the loading of high- and low-level data, respectively, from the shift-left serial input and the shifting of previously entered data one bit; data previously at  $Q_B$  is now at  $Q_A$ , the previous levels of  $Q_C$  and  $Q_D$  now are at  $Q_B$  and  $Q_C$ , respectively, and the data previously at  $Q_A$  no longer is in the register. This entry of serial data and shift takes place on the low-to-high transition of the clock when S1 is high and S0 is low, and the levels at inputs A through D have no effect.

The last row shows that, as long as both inputs are low, no other input has any effect and, as in the second row, the outputs maintain the levels they assumed before the steady-state combination of clear high and both mode inputs low was established.

The function table functional tests do not reflect all possible combinations or sequential modes.

#### 4.1.9 Logic Diagram

The logic diagram is a positive-logic illustration of the Boolean functionality of the device. Furthermore, in some logic-device data sheets that have wide identical configurations, such as a 16-bit or a 32-bit device, the logic diagram often is shown in partial format that includes the unique circuitry and only one of the data paths.

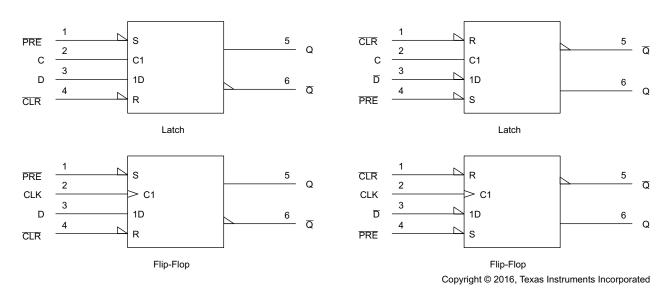

For D-type flip-flops and latches, it is TI convention to name the outputs and other inputs of a D-type flip-flop or latch and to draw its logic symbol, based on the assumption of true data (D) inputs. Outputs that produce data in phase with the data inputs are called Q, and those producing complementary data are called  $\overline{Q}$ . An input that causes a Q output to go high or a  $\overline{Q}$  output to go low is called preset (PRE). An input that causes a  $\overline{Q}$  output to go high or a Q output to go low is called clear (CLR). Bars are placed over these pin names (PRE and  $\overline{CLR}$ ) if they are active low.

The devices on several data sheets are second-source designs, and the pin-name conventions used by the original manufacturers have been retained. That makes it necessary to designate the inputs and outputs of the inverting circuits,  $\overline{D}$  and Q.

In some applications, it may be advantageous to re-designate the data input from D to  $\overline{D}$ , or vice versa. In that case, all the other inputs and outputs should be renamed, as shown Figure 27. Also shown, are corresponding changes in the graphical symbols. Arbitrary pin numbers are shown.

Figure 27. Example Logic Diagram

The figures show that when Q and  $\overline{Q}$  exchange names, the preset and clear pins also exchange names. The polarity indicators (  $\triangleright$  ) on  $\overline{PRE}$  and  $\overline{CLR}$  remain, as these inputs still are active low, but the presence or absence of the polarity indicator changes at D (or  $\overline{D}$ ), Q, and  $\overline{Q}$ . Pin 5 (Q or  $\overline{Q}$ ) is still in phase with the data input (D or  $\overline{D}$ ); their active levels change together.

#### 4.1.10 Product Development Stage Note

The product development stage note is a standard disclaimer placed at the lower left corner of the first page of data sheets, and the words **ADVANCED INFORMATION** or **PRODUCT PREVIEW**, as applicable, appear in the left and right margins of all pages of the data sheet. There is only the product development stage note on the first page for production-data devices. For additional information, see the EIA/JEDEC engineering publication, *Suggested Product-Documentation Classifications and Disclaimers*, JEP103A.

#### 4.1.11 Table Of Contents

The *Table of Contents* section provides the outline for the data sheet with each section and a hyperlink which when clicked to take directly to the specified page.

#### 4.2 Revision History

The changes for the data sheet compared to previous revision is mentioned in a tabular format along with the pages affected in the *Revision History*.

#### 4.3 Pin Configuration And Functions

Each of the packages top view or the bottom view (whenever applicable) is shown along with a tabular representation of the name of each pin , the pin position in each of the packages and the description of each pin. Each pin being input , output , Input /Output , power or ground pin is also mentioned in the same table.

#### 4.4 Absolute Maximum Ratings

#### 4.4.1 Supply Voltage, V<sub>cc</sub>

This is the maximum voltage that can be applied safely to the  $V_{CC}$  terminal, with respect to the ground of the device. However, no data sheet parameters are ensured when a device is operated at the absolute maximum  $V_{CC}$  level.

#### 4.4.2 Input Voltage, V<sub>1</sub>

This is the maximum voltage that can be applied safely to an input terminal, with respect to the ground of the device. This maximum  $V_1$  specification may be exceeded if the output clamp rating,  $I_{1K}$ , is observed.

#### Helpful Hint:

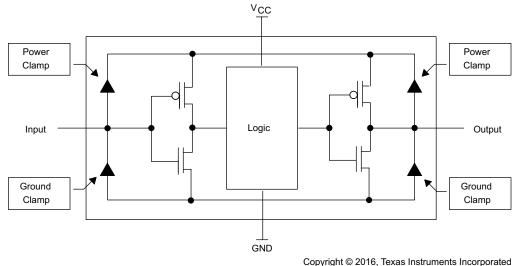

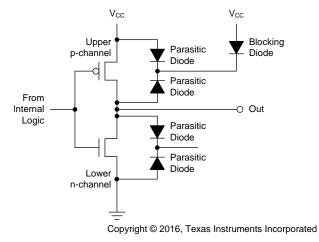

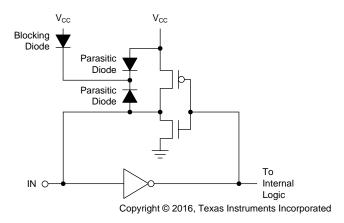

If there are clamp diodes between the device inputs and the  $V_{\rm CC}$  supply (see Figure 28) for ESD protection or overshoot clamping, the positive absolute-maximum rating for the input voltage is specified as  $V_{\rm CC}$  + 0.5 V. Keeping the applied input voltage less than 0.5 V above  $V_{\rm CC}$  ensures that there will not be enough voltage across the clamp diode to forward-bias it and cause current to flow through it. The TI logic families with clamp diodes in the inputs are: AC, ACT, AHC, AHCT, ALB, ALS, ALVC, AS, F, (CD)FCT, HC, HCT, HSTL, LS, PCA, PCF, S, SSTL, and TTL.

If there are no clamp diodes between the device inputs and the  $V_{CC}$  supply, the positive absolute maximum rating is a limitation of the process technology and is specified as an absolute voltage (for example, 5.5 V). The TI logic families without clamp diodes in the inputs are: ABT, ABTE, ALS, ALVT, AUC, AVC, BCT, FB, GTLP, GTL, LS, LV, LVC, LVCZ, LVT, (CY)FCT, SSTV, and VME.

You may exceed the negative input-voltage rating if you ensure that you are not putting too much current through the ground-clamp diode. The  $I_{IK}$  absolute maximum rating specifies the maximum current that may be put through the ground-clamp diode.

Copyright © 2016, Texas Instruments Incorporate

Figure 28. Representation of Typical Logic I/O Clamping Circuits

#### 4.4.3 Output Voltage, Vo

This is the maximum voltage that can be applied safely to an output terminal, with respect to the ground of the device.

#### Helpful Hint:

If there are clamp diodes between the device outputs and the  $V_{\rm CC}$  supply (see Figure 28) for ESD protection or parasitic current paths in the output p-channel pullup transistor, the positive absolute maximum rating for the output voltage is specified as  $V_{\rm CC}$  + 0.5 V. This ensures that there will not be enough voltage applied between the output and  $V_{\rm CC}$  to forward bias the clamp diode and cause current to flow. You may exceed the negative rating if you ensure that you are not putting too much current through the ground-clamp diode. The maximum current that you may put through the ground-clamp diode is specified in the  $I_{\rm OK}$  absolute maximum rating.

If there are no clamp diodes or parasitic current paths in the output P-channel pullup transistor between the device outputs and the  $V_{CC}$  supply, the positive absolute maximum rating is a limitation of the process technology and is specified as an absolute voltage.

#### 4.4.4 Voltage Range Applied to Any Output in the High-Impedance or Power-Off State, Vo

This specification is similar to the *Output Voltage*,  $V_{\rm O}$  specification and is used with the *Voltage Range Applied to Any Output in the High State*,  $V_{\rm O}$  specification. On devices with the  $I_{\rm off}$  feature, there are no clamp diodes or parasitic current paths in the output P-channel pullup transistor between the device outputs and the  $V_{\rm CC}$  supply; the positive absolute-maximum rating is a limitation of the process technology and is specified as an absolute voltage. You may exceed the negative rating if you ensure that you are not putting too much current through the ground-clamp diode. The maximum current that you may put through the ground-clamp diode is specified in the  $I_{\rm OK}$  absolute-maximum rating.

Helpful Hint:

This specification is necessary only for devices with the I<sub>off</sub> feature.

#### 4.4.5 Voltage Range Applied to Any Output in the High State, Vo

This specification is similar to the *Output Voltage*,  $V_{\rm O}$  specification and is used with the *Voltage Range Applied to Any Output in the High-Impedance or Power-Off State*,  $V_{\rm O}$  specification. When the output is enabled and is in the output high state, there is a current path between the output and  $V_{\rm CC}$  through the output P-channel pullup transistor. Applying a voltage to the output that is greater than the  $V_{\rm CC}$  voltage causes damaging current to flow back from the output into the  $V_{\rm CC}$  supply. You may exceed the negative rating if you ensure that you are not putting too much current through the power-clamp diode. The  $I_{\rm OK}$  absolute-maximum rating specifies the maximum current that you may put through the ground-clamp diode.

Helpful Hint:

This specification is necessary only for devices with the I<sub>off</sub> feature.

#### 4.4.6 Input Clamp Current, I<sub>IK</sub>

This is the maximum current that can flow safely into an input terminal of the device at voltages above or below the normal operating range.

Helpful Hint:

If there are clamp diodes between the device inputs and the  $V_{CC}$  supply (see Figure 28), for ESD protection or overshoot clamping, there will be both a positive and negative absolute maximum rating for the input clamp current. If there is only a negative absolute maximum rating, that implies that there is only a ground-clamp diode at the input, not a power-clamp diode.

#### 4.4.7 Output Clamp Current, I<sub>ok</sub>

This is the maximum current that can flow safely into an output terminal of the device at voltages above or below the normal operating range.

Helpful Hint:

If there are clamp diodes between the device outputs and the  $V_{CC}$  supply (see Figure 28), for ESD protection or parasitic current paths in the output P-channel pullup transistor, there will be both a positive and a negative absolute-maximum rating for the output clamp current. If there is only a negative absolute-maximum rating, that implies that there is only a ground-clamp diode at the output, not a power-clamp diode or a parasitic current path in the output P-channel pullup transistor.

#### 4.4.8 Continuous Output Current, Io

This is the maximum output source or sink current that can flow safely into an output terminal of the device at voltages within the normal operating range.

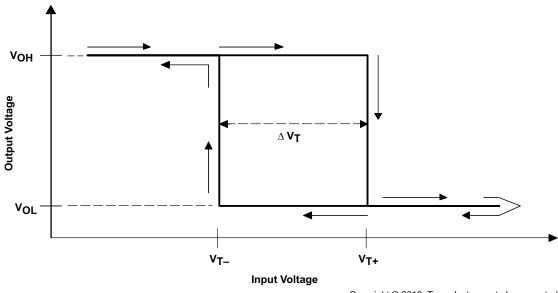

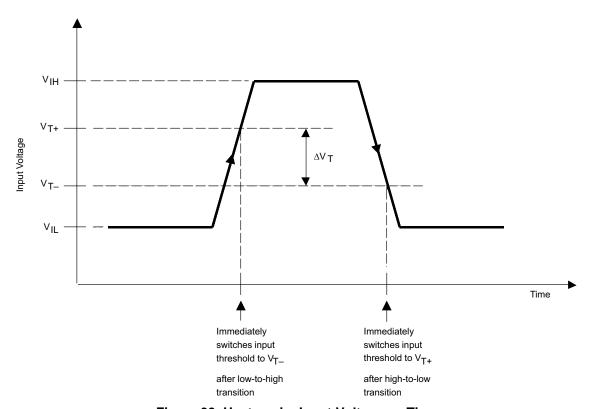

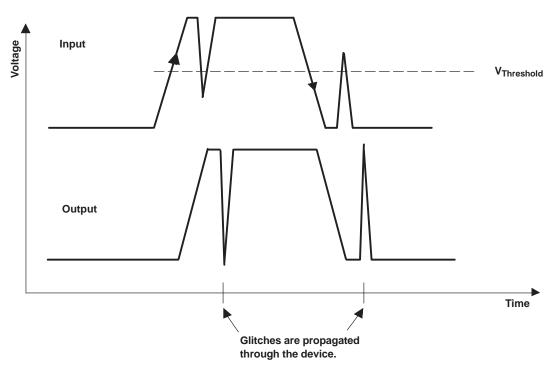

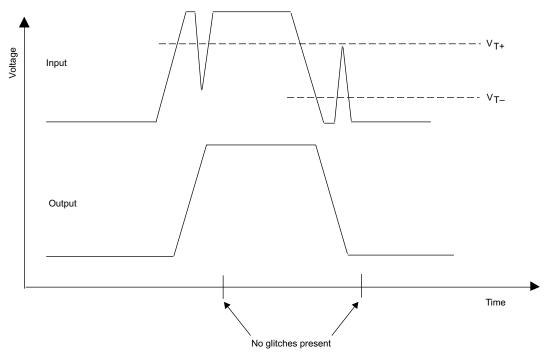

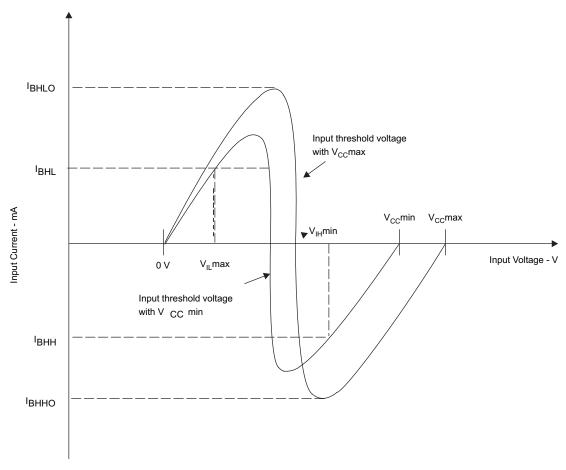

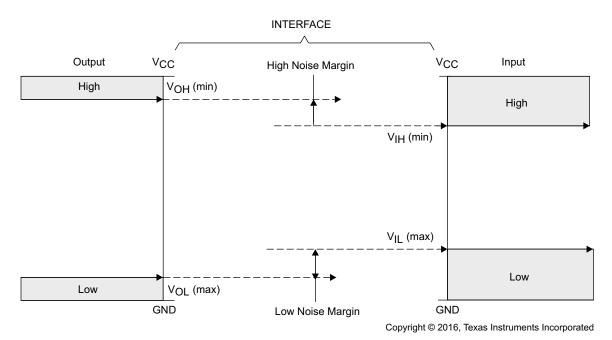

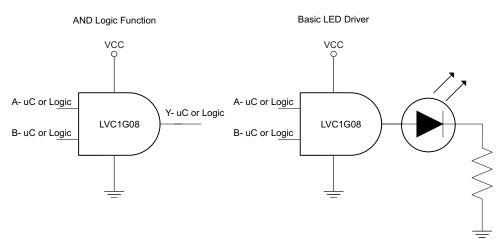

#### 4.4.9 Continuous Current Through V<sub>CC</sub> or GND Terminals