# TI Designs: TIDEP-0095 Virtualization: Jailhouse Hypervisor on AM572x Reference Design

# Texas Instruments

# Description

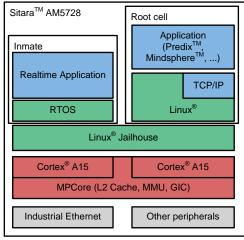

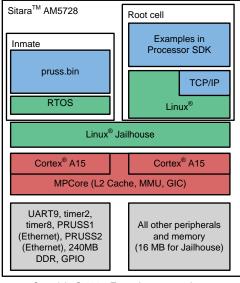

Industrial embedded systems are balancing traditional and proven real-time solutions based on bare-metal or real-time operating system (RTOS) with new requirements to add cloud connectivity and advanced graphical interfaces. Linux® is often the most efficient way to provide sophisticated, secure cloud connectivity and enable advanced, human to machine (HMI) interfaces. Modern embedded processors, such as Sitara<sup>™</sup> AM5728, offer the ability to integrate the functionality of a real-time application with Linux applications. This reference design uses the ARM® Cortex®-A15 cores and an open source, static hypervisor called Jailhouse to support the coexistence of real-time and Linux applications.

## Resources

| TIDEP-0095          | Design Folder  |

|---------------------|----------------|

| AM5728              | Product Folder |

| TMDXIDK5728         | Tools Folder   |

| TMDSEVM572X         | Tools Folder   |

| PROCESSOR-SDK-AM57X | Tools Folder   |

ASK Our E2E Experts

# Sitara<sup>™</sup> AM5728 Inmate Realtime Application RTOS Linux<sup>®</sup> Jailhouse Cortex<sup>®</sup> A15 MPCore (L2 Cache, MMU, GIC) Industrial Ethernet Other peripherals

Copyright © 2017, Texas Instruments Incorporated

TIDUDF8A-October 2017-Revised October 2017

Submit Documentation Feedback

#### Features

- Jailhouse Hypervisor Runs on Sitara AM572x With Linux on One ARM Cortex-A15 Core and Bare-Metal on Second Core

- Static Partitioning of AM572x Peripherals Between Linux and Bare-Metal

- Support to Run Bare-Metal Binary and RTOS-Based Binary on Second Core

- Performance (Interrupt Latency) Measurements for Virtualized Bare-Metal System With and Without Processing Load on Linux

- Tested on TMDXIDK5728 and TMDSEVM5728 Boards

#### Applications

- Factory Automation and Control—Programmable Logic Controller (PLC), DCS, and PAC—CPU (PLC Controller)

- Factory Automation and Control—HMI—Single Board Computer

- Grid Infrastructure—Protection Relay—Multi

Function Relay

- Grid Infrastructure—Grid Automation—Process Bus

- Grid Infrastructure Grid Automation System Bus

#### System Description

2

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information.

# 1 System Description

Embedded systems have different concerns and priorities from enterprise or data center server infrastructure or laptops. Typically the main difference is the priority of meeting the real-time requirement, as opposed to meeting a metric like average throughput or transactions per second. For embedded systems meeting the worst-case deadline is part of the correctness of the program, which is equally important to logical correctness. There is often no value in going beyond the required performance (for example, completing the task on average ahead of the deadline)or not meeting the required performance, which makes the system useless. In practice typical software (SW) architecture, such as RTOS or even a bare-metal-based periodic control loop triggered by either data input or a timer expiring, meets this requirement. Systems based on this pattern of SW architecture have been proven to work over the past several decades. Disrupting this established approach paradigm shifts, like Industry 4.0 and Industrial Internet of Things (IIoT), drive the requirement for a full-featured, cloud connectivity solution.

This solution has led many embedded systems to run Linux for the convenience of having a full-featured, networking stack with latest constantly updated security features and application-level protocols written in high-level languages like Python or Java. GE®'s Predix cloud platform and Siemens® Mindsphere® are examples of these protocols. However, for all the goodness of Linux, even with real-time (RT) patches, Linux might not satisfy the real-time constraints of toggling IO pins and counting nanoseconds. In these cases, being able to isolate a deterministic real-time OS or a bare-metal control loop alongside Linux is required. In some sense this is simpler than the traditional virtualization, which often has further goals beyond isolation, like consolidation of multiple-guest operating systems on to a single processor core or live migration of guests from a server or to another server. In embedded systems these use cases either do not exist or are of secondary value compared to meeting the real-time performance.

Using virtualization is not the only approach to design a system that combines a real-time application with a Linux application. A discrete solution with separate devices can sometimes make sense, but integrating the digital processing to one system-on-chip (SoC) brings size, communication latency, and often cost advantages. For some real-time applications using one or more of the embedded ARM Cortex-M4 or C66x DSP cores in the AM5728 SoC can be a more efficient solution than virtualizing a Cortex-A15 core. The right engineering tradeoff depends on the application, which includes the expected future evolution of additional features and capability. One alternative solution is moving the real-time application to RT Linux and using core affinity to assign the real-time threads to the second Cortex-A15 core while everything else is handled on the first core. The drawback with RT Linux is an order of magnitude higher worst case interrupt latency compared to an RTOS or a static hypervisor solution like Jailhouse.

#### 2 System Overview

This reference design is a template products that require the integration of a real-time component built using an RTOS and a Linux component, such as cloud connectivity or a graphics interface. An example of an RTOS application is a fieldbus protocol stack, such as PROFINET<sup>™</sup> or EtherCAT<sup>®</sup>. Linux Jailhouse manages boot and initialization of the system and peripherals using the two-stage hardware (HW) MMU isolates core 1 and the required peripherals for the inmate.

Copyright © 2017, Texas Instruments Incorporated

Figure 1. TIDEP-0095 Block Diagram

System Overview

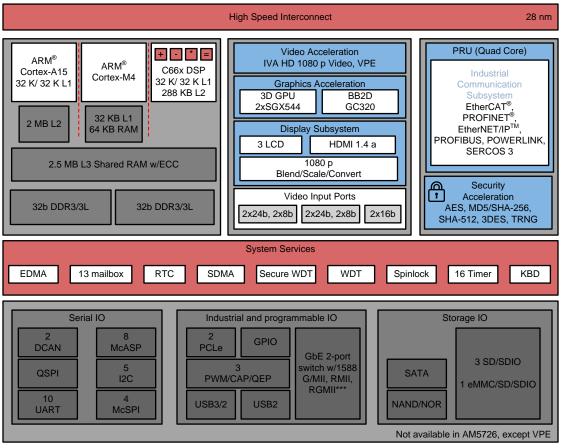

# 2.1 Multi-Core AM572x Processor

Copyright © 2017, Texas Instruments Incorporated

Figure 2. Sitara<sup>™</sup> AM5728 Block Diagram

The AM572x is a high-performance, Sitara processor based on two ARM Cortex-A15s and two TI C66x DSPs. TheAM572x is designed for embedded applications including PLCs, industrial network switches, industrial gateways for protocol translation, HMI, grid infrastructure protection and communications, and other industrial use applications. The device includes the following subsystems:

- ARM Cortex-A15 microprocessor unit (MPU) subsystem, including two ARM Cortex-A15 cores

- Two DSP C66x cores

- Two Cortex-M4 subsystems, each including two ARM Cortex-M4 cores

- Two dual-core PRU-ICSS (capable of industrial protocols such as EtherCAT, PROFINET, EtherNet/IP, PROFIBUS™, Ethernet POWERLINK, SERCOS III, HSR, PRP)

- · Graphics, video, real-time clock (RTC) and debug subsystems

The device supports memory management unit (MMU) and MPU:

- MMU used for key masters (Cortex-A15 MPU, Cortex-M4, C66x DSP, EDMA)

- Memory protection of C66x cores

- MMU inside the dynamic memory manager

The device also integrates:

• On-chip memory

**External Memory Faces:**

- Memory management

- Level 3 (L3) and level 4 (L4) interconnects

- System and serial peripherals

#### 2.2 Design Considerations

Jailhouse is a static partitioning hypervisor based on Linux. Jailhouse can run bare-metal applications or (adapted) operating systems aside from Linux. For this purpose, Jailhouse configures CPU and device virtualization features of the hardware platform in a way that none of these domains, called *cells*, can interfere with each other in an unacceptable way. The overriding approach in Jailhouse is optimization for simplicity rather than feature richness. Unlike full-featured, Linux-based hypervisors like KVM or Xen, Jailhouse does not support overcommitment of resources like CPUs, RAM, or devices. All hardware resources, such as memory, CPUs, and peripherals, are statically assigned to guest operating system. Jailhouse hypervisor performs no scheduling and only virtualizes resources in software that are essential for a platform and cannot be partitioned in hardware. An example of shared hardware with ARM Cortex-A based SoC's is the interrupt controller or GIC.

Once Jailhouse is activated, the hypervisor runs bare-metal, that is, it takes full control over the hardware and requires no external support. However, in contrast to other bare-metal hypervisors, Jailhouse is loaded and configured by a normal Linux system with a management interface based on Linux infrastructure. Boot Linux first, next enable Jailhouse, and finally split off parts of the system's resources and assign them to additional cells. In the case of AM5728, it only makes sense to have two cells, the root cell Linux on A15 core 0 and another cell typically running an RTOS or bare-metal on A15 core 1. Typically a real-time inmate would directly own a couple peripherals (for example, the industrial Ethernet port implementing a fieldbus). The rest of the peripherals, such as USB or displays, would be owned and used by standard Linux drivers. Networking peripherals would typically be shared—at a minimum—with the configuration part of the paravirtualized driver, which sets up the hardware, so at least the real-time traffic goes directly to the inmate's memory and best-effort, TCP traffic and any management traffic goes to the Linux networking stack. Jailhouse consists of three parts: kernel module, hypervisor firmware, and tools. These are used to enable the hypervisor, create a cell, load an inmate binary, run it and stop it. On AM572x, which has two ARM Cortex-A15 cores, Linux boots in SMP mode using both cores. After enabled, the hypervisor moves Linux to the root-cell. At this point the root cell still uses both ARM cores. When a new cell is created, the hypervisor calls cpu down() for the second core, which leaves Linux to run on core 0 only. The new cell will use core 1 and hardware resources dedicated for this cell in the cell configuration file.

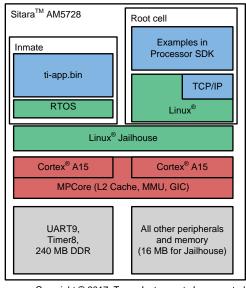

Jailhouse is based on static partitioning of memory and peripherals. On AM5728 one core will run Linux, and the inmate will run an RTOS or bare metal, which is managed with device tree. Those peripherals and memory allocated for the inmate are carved out with additional configuration to the Linux device tree. Section 3.1.1 describes the example device tree used in this reference where 240MB of physical memory, one timer, and one serial port (UART) are statically partitioned for the inmate. A further 16MB of memory is carved out for the hypervisor itself—primarily used to store the second stage virtual address translation page tables. The .cell configuration files are compiled files that describe the memory and peripherals allocated to the root-cell and each inmate.

#### 2.3 Highlighted Products

#### 2.3.1 TMDXIDK5728

The TMDXIDK5728 is the Sitara AM5728 industrial development kit (IDK) The TMDXIDK5728 can be used for both of the examples in this reference design and any application development that requires the usage of the programmable real-time units for industrial communication (PRU-ICSS). If developing HMI applications the display, TMDXIDK57X-LCD is also required. The single, Cortex-A15 core based AM571x and AM570x devices and evaluation boards are not applicable as Jailhouse requires two or more ARM Cortex-A cores.

The AM572x IDK is a development platform for evaluating the industrial communication and control capabilities of Sitara AM572x processors for applications in factory automation, drives, robotics, grid infrastructure, and more. AM572x processors include dual PRU-ICSS subsystems, which can be used for industrial Ethernet protocols, such as PROFINET, EtherCAT, Ethernet/IP, and others. The TMDXIDK5728 breaks out six ports of Ethernet, four of which can be used concurrently—2x Gb Ethernet ports and 2x 10/100 Ethernet ports from the PRU-ICSS subsystems.

#### 2.3.2 TMDSEVM572X

6

The TMDSEVM572X is the Sitara AM5728 general purpose evaluation module (GP-EVM). TMDSEVM572X can be used to run the UART and timer example application and for developing applications that do not require the use of the PRU-ICSS for industrial communication. The GP-EVM includes a display.

The AM572x EVM provides an affordable platform to quickly start evaluation of Sitara ARM Cortex-A15 AM57x processors (AM5728, AM5726, AM5718, AM5716) and accelerate development for HMI, machine vision, networking, medical imaging, and many other industrial applications. The EVM is a development platform based on the dual ARM Cortex-A15, dual C66x DSP processor that is integrated with tons of connectivity, such as PCIe, SATA, HDMI, USB 3.0 or 2.0, dual Gb Ethernet, and more.

The AM572x EVM also integrates video and 3D or 2D graphics acceleration as well as two PRU-ICSS and dual ARM Cortex-M4 cores.

## 2.4 System Design Theory

The peripherals will be owned by a inmate depending on the application. A good general principle is to keep the number of peripherals and amount of resources owned by the inmate as small as possible. This sizing is both to manage the complexity of meeting real-time and to minimize software engineering effort by using existing and maintained Linux drivers.

## 2.4.1 Example Device Tree

```

/* append to the existing device tree used with Linux, am57xx-evm-

reva3.dts is the device tree for the GP EVM */

#include "am57xx-evm-reva3.dts"

/* if you are using the IDK without a display use am572x-

idk.dts, if using an IDK with display use appropriate device tree file such as am572x-idk-lcd-

osd101t2045.dts */

/ {

reserved-memory {

/* reserve physical memory for the hypervisor privilege SW, 16MB (0x1000000) */

jailhouse: jailhouse@ef000000 {

reg = <0x0 0xef000000 0x0 0x1000000>;

no-map;

status = "okay";

};

/* reserve physical memory for the inmate SW, 256MB (0xF000000) */

jh_inmate: jh_inmate@ee000000 {

reg = <0x0 0xe0000000 0x0 0xf000000>;

no-map;

status = "okay";

};

};

};

/* assign timer8 to inmate, but allow Linux to configure clocking for it */

&timer8 {

status = "disabled";

ti,no-idle;

};

/* assign uart9 to inmate, but allow Linux to configure clocking for it */

&uart9 {

status = "disabled";

ti,no-idle;

};

/* configure the interrupt crossbar so the interrupts related to the above are not used by Linux.

Linux on AM5728 dynamically manages the interrupt crossbars, we want these to be statically

assigned to inmate */

/ {

ocp {

crossbar_mpu: crossbar@4a002a48 {

ti,irqs-skip = <10 133 134 135 139 140>;

};

};

};

```

#### 2.4.2 Sharing Peripherals

For some peripherals, such as Ethernet or storage, there is a requirement for both Linux and the real-time inmate to have access to the interface. To achieve this with Jailhouse, a paravirtualized driver is required. For example the real-time fieldbus, such as PROFINET, might be used for best-effort, Ethernet traffic coming from and going to the Linux networking stack. In this case the low-level control is typically in the real-time inmate with a paravirtualized Ethernet driver in the Linux side. In the case of storage, it might be more common to leverage the Linux driver and provide an interface for the inmate to read and write through a proxy application.

#### 3 Hardware, Software, Testing Requirements, and Test Results

#### 3.1 Required Hardware and Software

#### 3.1.1 UART and Timer Application Example

This section contains details of setting up Jailhouse on Sitara AM5728 with a bare-metal inmate on Cortex A15 core 1 and with Linux running on core 0. Further information on setting up Jailhouse can be found in *TI Processors Wiki*. The demonstration application is *ti-app*, which is a simple, forever loop that configures a timer and related interrupt, printing out values read from the timer periodically on the console (UART).

Copyright © 2017, Texas Instruments Incorporated

Figure 3. Bare Metal Application and Linux<sup>®</sup>

#### 3.1.1.1 Hardware

This example runs on AM5728 EVM and AM5728 IDK and a host Windows or Linux machine with Ethernet and USB. Connect a USB to serial port cable to the host and connect both host and the EVMto the same LAN. There are a couple slight differences between the AM5728 EVM and AM5728 IDK with or without a display are highlighted in parenthesis.

#### 3.1.1.2 Software

All the required software is in Processor SDK Linux 4.0.0 and can be run using the prebuilt SD card image. A Telnet and serial port console program, such as PuTTY, is required on the host. Source code for the application is located in */ti-processor-sdk-linux-am57xx-evm-04.00.00.04/board-support/extra-drivers/jailhouse-0.7/inmates/ti\_app/*.

- 1. Connect IDK and host to the same Ethernet LAN.

- 2. Connect serial to USB cable to the host. Check which COM port becomes visible when USB cable is connected from the host (typically COM3). Open a console with 115200 baud rate 8-1-none

- 3. Boot the EVM with the Processor SDK Linux 4.0.0 prebuilt SD card image.

- 4. Halt the boot with a key press to the console get to u-boot shell.

| www. | ti.com |

|------|--------|

|      |        |

- 5. Modify the boot arguments to use the correct device tree am572x-evm-jailhouse.dtb for the EVM (am572x-idk-jailhouse.dtb for the IDK without display, am572x-idk-jailhouse-lcd-osd101t2045.dtb, or am572x-idk-jailhouse-lcd-osd101t2587.dtb with display), and increase the contiguous virtual memory to for example 512M from the default 240M with environment variable vmalloc=512M. The device tree addition shown in Section 2.4.1 statically defines the memory used by jailhouse hypervisor and the inmate, and the interrupts and peripherals will be managed by the inmate. The contiguous memory is required to statically allocatargs\_mmce the memory (16MB for hypervisor, 16MB for inmate) for the inmate and hypervisor, and in 32-bit plafroms the typical default value is not sufficient. For the SD card binary with Processor SDK 4.0.0 these modifications can be done modifying args\_mmc by appending it with setenv args\_mmc \${args\_mmc} vmalloc=512M, and setenv findfdt 'setenv fdtfile am572x-evm-jailhouse.dtb'. Store the modifications with saveenv, and continue booting with the command boot.

- 5. Open a Telnet window to Linux on the EVM.

- 6. Next steps are to insert the kernel module, enable the hypervisor, create a cell for the inmate, load the bare metal binary, and start the binary. This is achieved with:

root@am57xx-evm:~# modprobe jailhouse root@am57xx-evm:~# jailhouse enable /usr/share/jailhouse/examples/am57xx-evm.cell root@am57xx-evm:~# jailhouse cell create /usr/share/jailhouse/examples/am57xx-evm-ti-app.cell root@am57xx-evm:~# jailhouse cell load 1 /usr/share/jailhouse/examples/ti-app.bin root@am57xx-evm:~# jailhouse cell start 1

The bare-metal example application is now running on core 1 and owns the UART, a timer, and related interrupts. Note the hypervisor sdebug messages will also print out on the serial port console in addition to the inmate. Linux continues to run utilizing cpu0 and has control over the rest of AM5728. This can be verified by launching any of the examples from the Matrix user interface, which will run in parallel to the inmate.

For example select *Video Analytics* and then *OpenCV+OpenCL+OpenGL* in Matrix to run an example application that utilizes the camera module, DSP offload, and the GPU. This and the other examples utilizing the Sitara AM5728 will continue to work with the ARM Cortex A15 core 1, a timer, and UART, which is carved out for the bare-metal inmate.

#### 3.1.2 RTOS-Based Application Example

This section contains details of setting up jailhouse on Sitara AM5728 with an RTOS-based inmate built external to Processor SDK Linux on Cortex A15 core 1 and with Linux running on core 0. Further information on setting up *jailhouse* can be found in *Processor SDK Jailhouse Hypervisor*. The demonstration application is a TI RTOS-based application *pruss* loading the test application from Processor SDK RTOS to the programmable real-time units (PRUs). The PRU is a programmable building block inside the industrial communications subsystem (ICSS) that can be used to implement Ethernet or serial communication based fieldbusses (such as EtherCAT, PROFINET IRT, or PROFIBUS) or other functions requiring the lowest possible latency. This test is intended to show how a binary built outside Linux and utilizing an RTOS can be used. The test application loads simple firmware to the two PRUs, uses a timer, exchanges interrupts with the PRUs, and prints this out using the UART.

Copyright © 2017, Texas Instruments Incorporated

Figure 4. RTOS and Linux With Jailhouse Hypervisor

#### 3.1.2.1 Hardware

This example runs on AM5728 IDK and a host Windows or Linux machine with Ethernet and USB. Connect a USB to serial port cable to the host and connect both host and the EVM to the same LAN.

#### 3.1.2.2 Software

All the required software is in Processor SDK Linux 4.0.0 and can be run using the prebuilt SD card image. A Telnet and serial port console program, such as PuTTY, is required on the host.Processor SDK RTOS 4.0.0 is used as the RTOS, and the test application for PRUs is used as the test application. The example application source code is in */ti/pdk\_am57xx\_1\_0\_7/packages/ti/drv/pruss/test*. There are couple modifications needed to run this application as an inmate are limited to removing initialization related to UART, GIC, and the IO delays which are covered by Linux in the Jailhouse case. The source code for these modifications and makefile is in */ti/processor\_sdk\_rtos\_am57xx\_4\_00\_00\_04/demos/jailhouse-inmate/rtos/pru-icss*.

**NOTE:** Update the path name will change if using a newer Processor SDK release.

The TI RTOS configuration file, bios/pruss\_arm\_wSoCLib.cfg related, and board initialization file, src/idkAM572x\_jh.c, have been modified to remove the initialization for the board already covered by Linux. For details compare to the stand alone RTOS version located in /ti/pdk\_am57xx\_1\_0\_7/packages/ti/drv/pruss/test/am572x/armv7/bios/.

10 Virtualization: Jailhouse Hypervisor on AM572x Reference Design

Build the pruss application to be used as inmate (pruss.bin is not included in the Processor SDK Linux):

1. Go to /processor\_sdk\_rtos\_am57xx\_4\_00\_00\_04.

**NOTE:** Update the path name will change if using a newer Processor SDK release.

- 2. Type: source setupenv.sh to set up environment variables related to compiling.

- 3. Go to /processor\_sdk\_rtos\_am57xx\_4\_00\_00\_04/demos/jailhouse-inmate.

NOTE: Update the path name will change if using a newer Processor SDK release.

- 4. Type: source setenv.sh to set up environment variables related to the pruss application.

- 5. Run: make pruss\_test.

- 6. Copy pruss.bin to /usr/share/jailhouse/examples/ directory on the IDK

Run the pruss application:

- 1. Connect IDK and host to the same Ethernet LAN.

- 2. Connect serial to USB cable to the host. Check which COM port becomes visible when USB cable is connected from the host (typically COM3), and open a console with 115200 baud rate 8-1-none.

- 3. Boot the EVM with the Processor SDK 4.0.0 prebuilt SD card image.

- 4. Halt the boot with a key press to the console get to u-boot shell.

- 5. Modify the boot arguments to use the correct device tree am572x-idk-jailhouse.dtb for IDK without a display (am572x-idk-jailhouse-lcd-osd101t2045.dtb or am572x-idk-jailhouse-lcd-osd101t2587.dtb with display) and increase the contiguous virtual memory to for example 512M from the default 240M with environment variable vmalloc=512M. The device tree addition statically defines the memory used by jailhouse hypervisor and the inmate and which interrupts and peripherals will be managed by the inmate. The contiguous memory is required to statically allocate the memory (16MB for hypervisor, 16MB for inmate) for the inmate and hypervisor, and in 32-bit platforms, the typical default value is not sufficient. For the SD card binary with Processor SDK 4.0.0 these modifications can be done modifying args\_mmc by appending it with setenv args\_mmc \${args\_mmc} vmalloc=512M and setenv findfdt 'setenv fdtfile am572x-idk-jailhouse.dtb'. Store the modifications with saveenv, and continue booting with the command boot.

- 6. Open a Telnet window to Linux on the EVM.

- 7. Next steps are to insert the kernel module, enable the hypervisor, create a cell for the inmate, load the bare metal binary, and start the binary. The inmate will see intermediate physical addresses (IPA) as opposed to physical addresses. Depending on the RTOS used this might require some startup code to get running with Jailhouse. TI RTOS based binary expects to be loaded to address 0x80000000, which is the beginning of the DDR on AM572x while Jailhouse loads the program to address 0x0 in IPA address space. linux-loader.bin is a helper program that itself is loaded to address 0x0 and contains a branch to the entry point of the TI RTOS based image (0x80005128, passed to linux-loader.bin with a string at address 0x100). This is achieved with:

```

root@am57xx-evm:~# modprobe jailhouse

root@am57xx-evm:~# jailhouse enable /usr/share/jailhouse/examples/am57xx-evm.cell

root@am57xx-evm:~# jailhouse cell create /usr/share/jailhouse/examples/am572x-rtos-pruss.cell

root@am57xx-evm:~# jailhouse cell load 1 linux-loader.bin -a 0 -s "kernel=0x80005128" -

a 0x100 pruss.bin -a 0x80000000

root@am57xx-evm:~# jailhouse cell start 1

```

The RTOS example application pruss is now running on core 1 and will print out status messages on the UART. Linux continues to run using core 0 and the rest of AM5728. This can be verified by running Linux applications from the Telnet shell or with a display, by launching them from the Matrix GUI.

#### 3.2 Testing and Results

#### 3.2.1 Test Setup

To verify the real-time performance of Jailhouse Sitara AM5728 was setup to run Linux on one of the ARM Cortex A15 cores and a TI-RTOS inmate on the other A15 core. A test was run to measure interrupt latency. Poll mode driver based application performance of an inmate should be identical to a system without virtualization in a static partitioning system like Jailhouse. Anything interrupt-based is required to share the interrupt controller (GIC), which will introduce some interference from Linux to the real-time application. The measurements shown in Section 3.2.2 a million interrupts clearly shows the interference and captures the upper bound at 8.8 µs. For the first run of interrupt latency test an unloaded Linux running on core 0 is in the first column. In the second column Linux on core 0 is running STREAM. STREAM is an external memory access benchmark that fully uses the number of outstanding reads and writes to memory. The benchmark is scalable from individual processors to clusters supercomputers and is used at the processor level. STREAM was chosen as representative of a worst case memory access behavior of a Linux-based application on a Cortex A15, essentially with a memory access profile like an optimized memoryto-memory copy. In AM5728 the two Cortex-A15 cores share L2 cache and access to the rest of the SoC, which the STREAM benchmark running on core 0 stresses while core 1 access GIC registers to respond to the interrupt.

#### 3.2.2 Test Results

#### 3.2.2.1 Jailhouse Performance on Sitara<sup>™</sup> AM5728

|                                             | UNLOADED LINUX ON CORE 0 | LINUX RUNNING STREAM<br>BENCHMARK ON CORE 0 |

|---------------------------------------------|--------------------------|---------------------------------------------|

| Interrupt count<br>Bucket 1.6 μs to 3.2 μs  | 99.3756%                 | 33.9323%                                    |

| Interrupt count<br>Bucket 3.2 μs to 6.4 μs  | 0.6244%                  | 66.0632%                                    |

| Interrupt count<br>Bucket 6.4 µs to 12.8 µs | none                     | 0.0045%                                     |

| Minimum interrupt latency                   | 2.2 ms                   | 1.8 ms                                      |

| Maximum interrupt latency                   | 5 ms                     | 8.8 ms                                      |

#### Table 1. Interrupt Latency Of A Bare Metal Inmate (Core 1)

#### 4 Software Files

- Processor SDK Linux 4.00.00.04

- Prebuilt SD card image can be used.

- Processor SDK RTOS 4.00.00.04

- pruss example is used as an example inmate built outside Linux using TI RTOS

# 5 Related Documentation

1. STREAM Benchmark

# 5.1 Trademarks

Sitara is a trademark of Texas Instruments. ARM, Cortex are registered trademarks of ARM Limited. EtherCAT is a registered trademark of Beckhoff Automation GmbH. GE is a registered trademark of General Electric Compay. Linux is a registered trademark of Linux Foundation. PROFINET, PROFIBUS are trademarks of PROFIBUS and PROFINET International (PI). Siemens, Mindsphere are registered trademarks of Siemens AG. All other trademarks are the property of their respective owners.

# 6 Terminology

- GIC—generic interrupt controller

- GUI-graphical user interface

- MMU—memory management unit

- MPCore—multi processor core, a cluster of ARM Cortex A cores with a shared cache

- SoC—System on Chip

# 7 About the Author

PEKKA VARIS is the Chief Technologist for Catalog Processors Business in Texas Instruments.

**VITALY ANDRIANOV** is a Software Engineer in the the Processor SDK Linux team who has implemented Jailhouse support for the Sitara processors.

Revision A History

#### www.ti.com

Page

# **Revision A History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Original (October 2017) to A Revision

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated